XX (113552.1)

# CINVESTAV

Centro de Investigación y de Estudios Avanzados del I.P.N. Unidad Guadalajara

# Diseño de Inductores Integrados Flotantes Para Aplicaciones en RF.

Tesis que presenta: Luis Flores Gómez IPN

ADQUISICION

DE LIBROS

para obtener el grado de: Maestro en Ciencias

en la especialidad de: Ingeniería Eléctrica

Director de Tesis

Dr. Federico Sandoval Ibarra

CINVESTAV I.P N. SECCION DE INFORMACION Y DOCUMENTACION

CLASIF.: 1K165.68 F56 2003 ADQUIS.: SS1 - 313 FECHA: 28 - V1 - 2004 PROCED.: 1001 - 7004

\* 9

10:113628-2001

# Diseño de Inductores Integrados Flotantes Para Aplicaciones en RF.

# Tesis de Maestría en Ciencias Ingeniería Eléctrica

Por:

Luis Flores Gómez

Ingeniero en Electrónica con Especialidad en Sistemas Digitales

Instituto Tecnológico de Hermosillo 1996-2001

Becario del CONACyT, expediente no. 165091

Director de Tesis **Dr. Federico Sandoval Ibarra**

# **Contenido**

| Introducción General                                                                                                           | 1      |

|--------------------------------------------------------------------------------------------------------------------------------|--------|

| Características de la inductancia                                                                                              | 4      |

| No idealidades del inductor                                                                                                    | 5      |

| Inuductancia propia, e Inductancia mutua                                                                                       | 5      |

| Dimensiones                                                                                                                    | 5      |

| Capacitancia Parásita                                                                                                          | د<br>6 |

| Frecuencia de Auto resonancia (SFR)                                                                                            |        |

| Factor de Calidad (Q)                                                                                                          |        |

| Potencia Máxima                                                                                                                |        |

| Importancia de los inductores                                                                                                  | 9      |

| Inductores en amplificadores de alta frecuencia                                                                                | 9      |

| Inductores en LNA's.                                                                                                           |        |

| Amplificadores sintonizados                                                                                                    |        |

| •                                                                                                                              |        |

| Referencias.                                                                                                                   |        |

| Capitulo 1                                                                                                                     | 15     |

| Inductores Completamente Integrados en Silicio                                                                                 | 15     |

| 1.1 Características de inductores integrados.                                                                                  | 16     |

| 1.2 Cálculo de los efectos parásitas                                                                                           | 16     |

| 1.3 Cálculo del valor de inductancia                                                                                           | 19     |

| 1.4 Resultados de los cálculos.                                                                                                | 21     |

| Capitulo 2                                                                                                                     | 24     |

| Revisión de Trabajos Existentes                                                                                                | 24     |

| 2.1 Silicio como material base de RF.                                                                                          | 25     |

| 2.2 Trabajos Previos.                                                                                                          | 26     |

| 2.2.1 proceso de fabricación utilizado para disminuir efectos parásitos                                                        | 26     |

| 2.2.2 Diseño y fabricación de inductores con tecnología AT&T CBIC-2                                                            |        |

| 2.2.3 Aproximación para analizar inductores y transformadores en silicio.      2.2.4 Inductor integrado sobre escudo ranurado. |        |

| 2.2.5 Parámetros incluidos en un inductor integrado.                                                                           |        |

| 2.2.6 Estudio sobre la disminución de perdidas por substrato.                                                                  |        |

| 2.2.7 Nuevo modelo físico del inductor.                                                                                        | 30     |

| 2.2.8 Método para alcanzar altos valores de Q.                                                                                 | 30     |

| 2.2.9 Fabricación de inductores tridimensionales.                                                                              |        |

| 2.2.10 Fabricación de micro inductores de dos capas verticales en cobre                                                        | 31     |

| 2.2.11 Fabricación de inductores multi-capa 3-D      2.2.12 Nuevo modelo físico del inductor          |            |

|-------------------------------------------------------------------------------------------------------|------------|

| Referencias                                                                                           |            |

| Capitulo 3                                                                                            |            |

| Tecnología de Circuitos Integrados                                                                    |            |

| 3.1 Micro maquinado de superficie                                                                     |            |

| 3.2 Oxidación.                                                                                        |            |

| 3.3 Metalización                                                                                      |            |

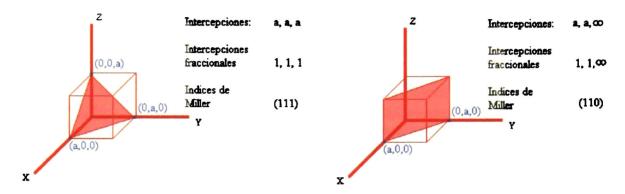

| 3.4 Proceso de fotolitografía.                                                                        | 39         |

| 3.5 Grabado de Aluminio.                                                                              | 41         |

| 3.6 Grabado de Silicio                                                                                | 43         |

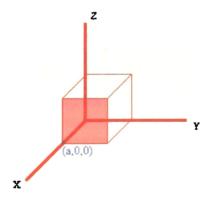

| 3.7 Índices de Miller                                                                                 | <b>4</b> 4 |

| 3.8 Soluciones de Grabado                                                                             | 45         |

| Capitulo 4                                                                                            | 47         |

| Proceso de Fabricación                                                                                | 47         |

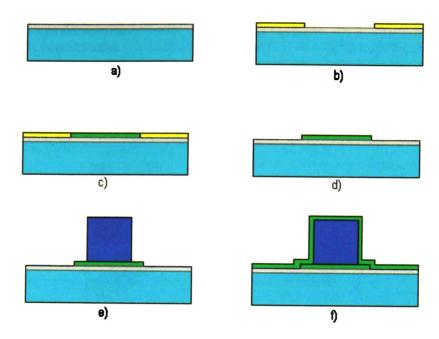

| 4.1 Estrategia de diseño                                                                              | 47         |

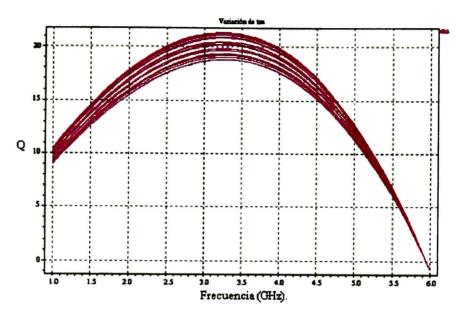

| 4.3 Análisis MonteCarlo del inductor                                                                  | 50         |

| 4.4 Esfuerzo mecánico en micro estructuras                                                            | 51         |

| 4.5 Introducción a los comportamientos mecánicos                                                      | 52         |

| 4.6 Propiedades mecánicas de los materiales 4.6.1 Elasticidad 4.6.2 Viscosidad 4.6.3 Viscoelasticidad | 53<br>53   |

| 4.7 Estrés térmico.                                                                                   | 53         |

| 4.8 Efecto de dopantes en Silicio                                                                     | 54         |

| 4.9 Proceso de Interferometría                                                                        | 55         |

| _4.10 Comentarios finales                                                                             | 56         |

| Capitulo 5                                                                                            |            |

| Conclusiones                                                                                          |            |

| 5.1 Conclusiones de la tesis                                                                          | 58         |

| 5.2 Trabajo futuro                                                                                    | 50         |

# Índice de Figuras

## Introducción General

| Fig. 0. 1 Inductor de espira circular. En su forma más simple, es un dispositivo de dos terminales                        |

|---------------------------------------------------------------------------------------------------------------------------|

| formado por un alambre conductor embobinado1                                                                              |

| Fig. 0. 2 Símbolos esquemáticos de inductores2                                                                            |

| Fig. 0. 3 Inductores con núcleo de aire y de hierro                                                                       |

| Fig. 0. 4 Inductores con diferente número de espiras.                                                                     |

| Fig. 0. 5 Inductores con diferente área4                                                                                  |

| Fig. 0. 6 Inductores con diferente longitud.                                                                              |

| Fig. 0. 7 Inductor con sus capacitancias parásitas                                                                        |

| Fig. 0. 8 En (a) se muestra una corriente I circulando a través de un conductor a baja frecuencia,                        |

| mientras que en (b) se ilustra el efecto skin en un conductor cuando la corriente fluye a muy alta                        |

| frecuencia. c) y d) muestran un corte de sección transversal en la dirección x de a) y b)                                 |

| respectivamente7                                                                                                          |

| Fig. 0. 9 Modelo equivalente del inductor.                                                                                |

| Fig. 0. 9 Modelo equivalente del inductor.                                                                                |

|                                                                                                                           |

| Fig. 0. 11 Variación de Q en un inductor vs. frecuencia.                                                                  |

| Fig. 0. 12 Amplificador Shunt-Peaked. La capacitancia C representa la carga en el nodo de salida; la                      |

| resistencia R es la carga efectiva y el inductor L provee el incremento del ancho de banda                                |

| Fig. 0. 13 Modelo en pequeña señal del amplificador Shunt-Peaked                                                          |

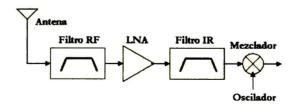

| Fig. 0. 14 Bloque básico de un receptor                                                                                   |

| Fig. 0. 15 LNA de banda angosta con degeneración inductiva en la fuente                                                   |

| Fig. 0. 16 Amplificador de fuente común con sintonizador de carga                                                         |

| Fig. 0. 17 a) Inductor activo [5], b) Inductor pasivo planar cuadrado [6],                                                |

|                                                                                                                           |

| Capitulo 1                                                                                                                |

|                                                                                                                           |

| Fig. 1. 1 a) Cuadrada, b) Hexagonal, c) Octagonal, d) Circular. Tradicionalmente el material usado                        |

| es aluminio, el cual es aislado del material semiconductor mediante una película de óxido de silicio                      |

| de muy alta calidad (SiO <sub>2</sub> térmico)                                                                            |

| Fig. 1. 2 capacitancia en serie $C_s$ , capacitancia del oxido $C_{ox}$ , $C_{si}$ y $R_{si}$ representan la capacitancia |

| y la resistencia del substrato, R <sub>s</sub> resistencia en serie, y L <sub>s</sub> Inductancia                         |

| Fig. 1. 3 Parámetros típicos de una espira conductora                                                                     |

| Fig. 1. 4 Definición de GMD.                                                                                              |

| Fig. 1. 5 Conductores paralelos de una espira                                                                             |

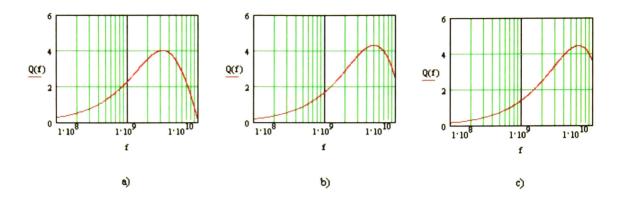

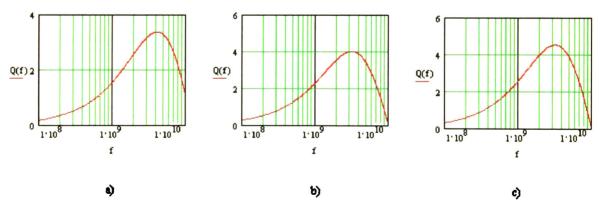

| Fig. 1. 6 Gráficas de Q contra frecuencia a) N=3, b) N=7, c) N=921                                                        |

| Fig. 1. 7 Gráficas de Q contra frecuencia a) s =4 $\mu$ m, b) s =8 $\mu$ m, c) s =10 $\mu$ m                              |

| Fig. 1. 8 Gráficas de Q contra frecuencia a) w =3 $\mu$ m , b) w =6 $\mu$ m, c) w =9 $\mu$ m                              |

| Capitulo 2                                                                                                                |

|                                                                                                                           |

| Fig. 2. 1 Modelo del inductor publicada en [2]                                                                            |

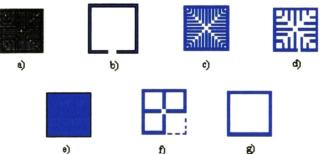

| Fig. 2. 2 a) inductor sin escudo de protección, b) escudo de protección sólido, c) escudo de                  |      |

|---------------------------------------------------------------------------------------------------------------|------|

| protección con ranurada                                                                                       | . 28 |

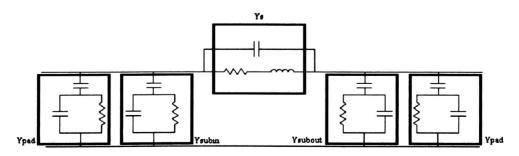

| Fig. 2. 3 Circuito equivalente del inductor incluyendo los pads de medición                                   | . 28 |

| Fig. 2. 4 a) escudo perforado (PG). b) substrato halo (HG). c) escudo con patrón de barra delgada             |      |

| (NBP). d) patrón de barra ancha (WBP). e) escudo sólido (SG). f) patrón de barra cruzada (CBP)                |      |

| substrato sin escudo (NG).                                                                                    | . 29 |

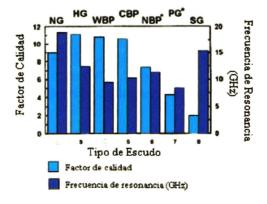

| Fig. 2. 5 Resultados de los diferentes escudos utilizados.                                                    |      |

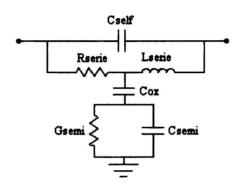

| Fig. 2. 6 Modelo equivalente del inductor según [7]                                                           |      |

| Fig. 2. 7 a) sección transversal y b) vista superior de un inductor                                           |      |

| Fig. 2. 8 Proceso de fabricación utilizado por [9]                                                            |      |

| Fig. 2. 9 Inductor propuesto en [11].                                                                         |      |

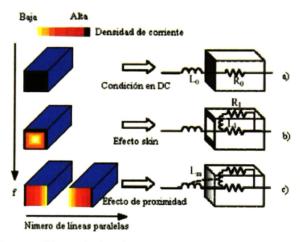

| Fig. 2. 10 Fenómenos físicos relacionados con una pista conforme aumenta la frecuencia                        |      |

| Fig. 2. 11 Modelo completo propuesto por [12]                                                                 |      |

| G                                                                                                             |      |

| Capitulo 3                                                                                                    |      |

| Cupitulo 5                                                                                                    |      |

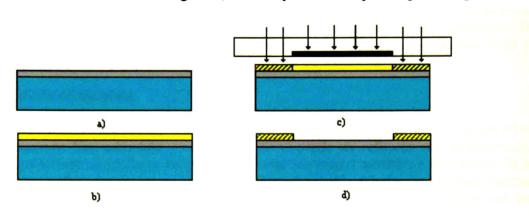

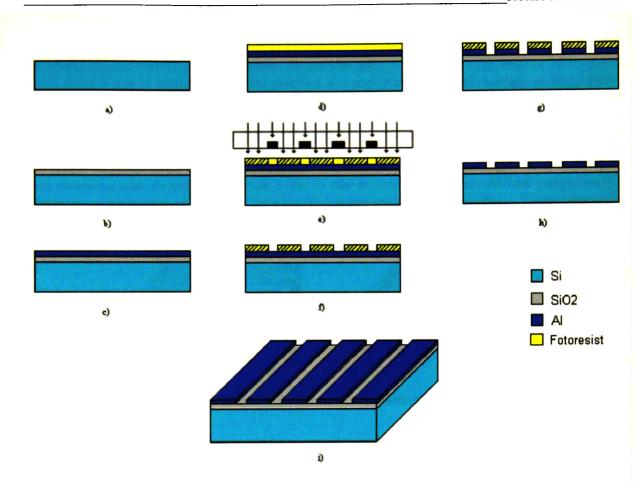

| Fig. 3. 1 Definición y transferencia de un patrón geométrico de Al sobre Si                                   | 36   |

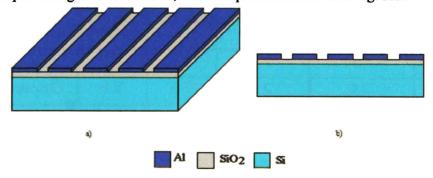

| Fig. 3. 2 a) Dióxido de silicio sobre Si b) Aluminio sobre dióxido de Si                                      |      |

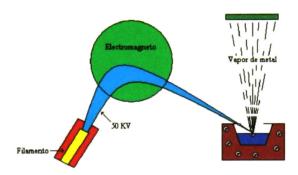

| Fig. 3. 3 Diagrama esquemático del proceso de evaporación con haz de electrones                               |      |

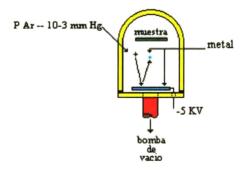

| Fig. 3. 4 Diagrama esquemático del proceso de sputtering.                                                     |      |

| Fig. 3. 5 Pasos para definir una ventanilla en una película de óxido sobre silicio mediante                   | . 37 |

| fotolitografiafotolitografia                                                                                  | 40   |

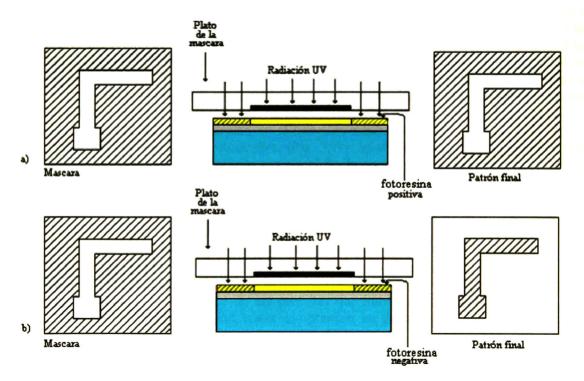

| Fig. 3. 6 a) Fotolitografía utilizando resina positiva b) Fotolitografía utilizando resina negativa           |      |

| Fig. 3. 7 Proceso necesario para definir un patrón de Al sobre un óxido de silicio                            |      |

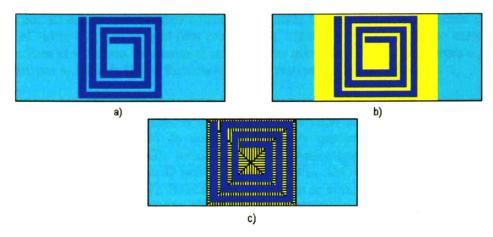

| Fig. 3. 8 Inductor pasivo completamente integrado de Al sobre una capa de SiO <sub>2</sub> que su vez está    | . 42 |

|                                                                                                               | 40   |

| sobre una de SiFig. 3. 9 Inductor integrado flotante a) Utilizando capa de sacrificio. b) micro maquinando el | 42   |

|                                                                                                               | 42   |

| substrato                                                                                                     |      |

| Fig. 3. 10 Tipos de grabado                                                                                   |      |

| Fig. 3. 12 Índices de Miller (111), b) (110)                                                                  | 45   |

| Fig. 3. 13 Grabado de Si con KOH                                                                              | 46   |

|                                                                                                               |      |

| Capitulo 4                                                                                                    |      |

| Fig. 4.1 Co-1-4                                                                                               |      |

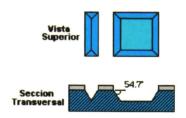

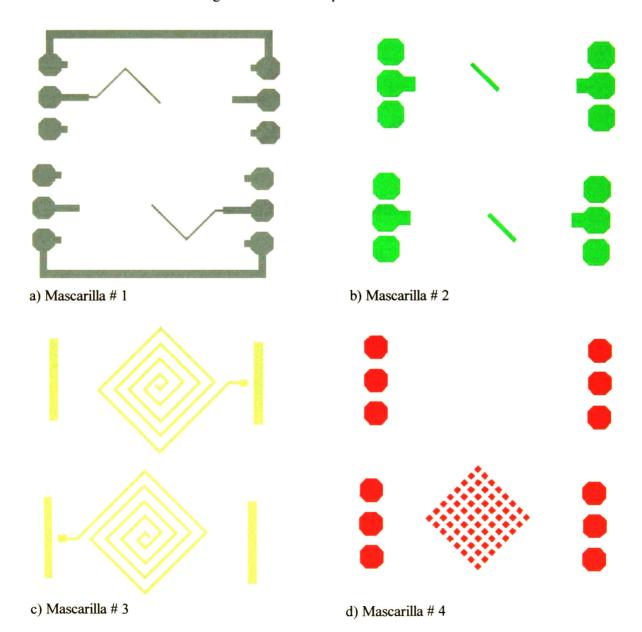

| Fig. 4. 1 Grabado anisotrópico en una oblea de silicio (100) con máscaras en diferentes                       |      |

| orientaciones.                                                                                                | 47   |

| Fig. 4. 2 (a) Patrón básico usado para desarrollar una rejilla flotante. (b) Resultados experimentale         | S    |

| que corroboran la técnica propuesta.                                                                          | 48   |

| Fig. 4. 3 Silicio entre substrato y una máscara de silicio.                                                   | 48   |

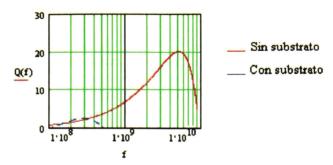

| Fig. 4. 4 Resultados de simulación indicando que la razón del bajo valor del factor de calidad es             |      |

| debido a la pérdida por substrato                                                                             | 49   |

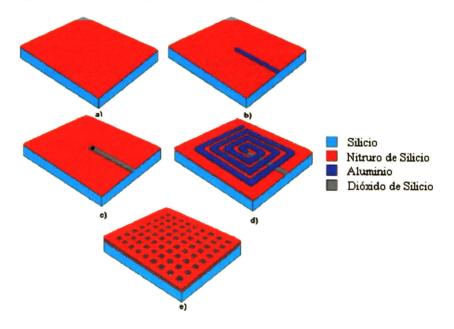

| Fig. 4. 5 Secuencia del proceso de fabricación de la espira.                                                  | 49   |

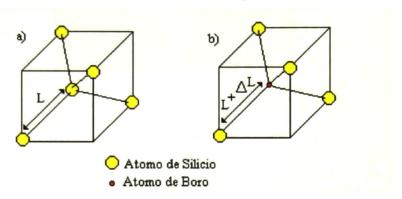

| Fig. 4. 10 Ilustración tridimensional de la deformación de la red cristalina debido a boro                    | 54   |

| Fig. 4. 11 Para la obtención de las estructuras de prueba se usó Hidróxido de tetrametil amonio               |      |

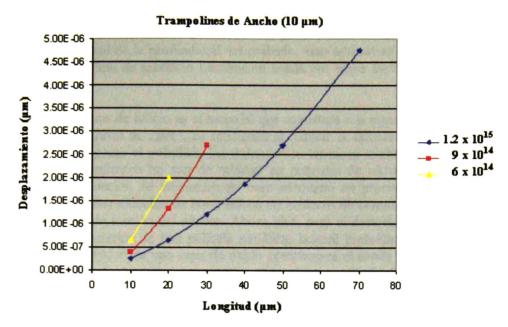

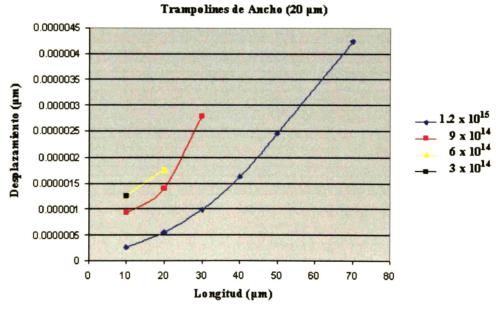

| (TMAH) al 2.5% con 0.29 mol/lt de silicio disuelto. La temperatura de grabado fue 80 °C                       | 55   |

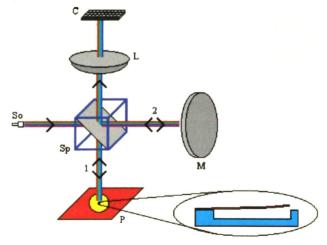

| Fig. 4. 12 Interferometro Michelson.                                                                          | 55   |

# Índice de Tablas

| _   |     |      |     | ~    |      |

|-----|-----|------|-----|------|------|

| I m | POC | HAAL | Ó.D | Gen  | aral |

| 111 | uvu | ucc  | UII | UCII | ciai |

| Tabla 0. 1 Algunos materiales utilizados en el núcleo de inductores [8]                        | 3          |

|------------------------------------------------------------------------------------------------|------------|

| Tabla 0. 2 Valores típicos de K dependiendo de la relación λ/D                                 | 6          |

| Tabla 0. 3 Resistividad de algunos materiales. ¿cuál es el más utilizado y por qué?            | 6          |

| Tabla 0. 4 Especificaciones de diseño.                                                         | 12         |

| Capitulo 1                                                                                     |            |

| Tabla 1. 1 Resultados de la simulación con el método de Greenhouse variando N                  | 21         |

| Tabla 1. 2 Resultados de la simulación con el método de Greenhouse variando s                  | 21         |

| Tabla 1. 3 Resultados de la simulación con el método de Greenhouse variando w                  | 22         |

| Capitulo 2                                                                                     |            |

| Tabla 2. 1 Propiedades físicas de algunos materiales                                           | 25         |

| Capitulo 3                                                                                     |            |

| Tabla 3. 1 Comparación de los diferentes procesos crecimiento/deposición de dióxido de s       | ilicio37   |

| Tabla 3. 2 Análisis de in inductor variando el grosor del óxido, el grosor del óxido entre med | tales y la |

| separación del óxido al sustrato                                                               | 42         |

| Tabla 3, 3 Características de algunas soluciones de grabado                                    | 45         |

# **Agradecimientos**

En los dos últimos años, he tenido la suerte de trabajar con gente que me ha ayudado de una u otra manera, tanto en el intenso y estimulante trabajo de la investigación, como apoyándome moralmente. En esta hoja voy a tratar de agradecer dicha ayuda. Es dificil para mi expresar la gratitud que siento en pocas palabras, pero lo voy a intentar.

En primera instancia y mas importante, expreso mi más sincero agradecimiento a Dios, ya que creo que él, es el que a estado siempre a mi lado dándome fuerzas para seguir adelante con mis estudios.

Gracias también al Dr. Federico Sandoval Ibarra por su paciencia y por haberme guiado de manera excelente durante la investigación.

A mis amigos Rubén Blanco Avilés, Martín Enrique Barrera Cerda, Sergio González Velásquez, Fabián Castañón Sotelo, Ricardo Usiel Chávez Cuadras les agradezco también el haberme dado su apoyo, tanto moral, como en lo que a conocimientos concierne y por haber estado ahí cuando yo los necesitaba.

Un agradecimiento para el Centre Nacional de Microelectrónica CNM (CSIC) en Barcelona, España, por las facilidades otorgadas para la fabricación de las estructuras de prueba. De igual manera un agradecimiento sincero para J. Esteve, I. Gràciay en especial a M. Duch por su asistencia en el proceso de grabado húmedo.

La asistencia técnica del personal del Laboratorio de Microelectrónica del INAOE en Tonantzintla, Puebla, fue fundamental para llevar acabo las pruebas de grabado de silicio. Para todos ellos un agradecimiento sincero.

Al CONACYT por su invaluable apoyo económico ya que sin el habría sido muy dificil concluir con mis estudios de maestría.

Al final pero no por eso menos importante, quiero agradecer el apoyo recibido de mi familia entera, especialmente de mis padres Luis Flores Gómez y Florencia Gómez de Flores y de mis hermanos Joel de Jesús Flores y Antonio Flores. También quiero expresar mi gratitud por el amor, paciencia y confianza que me ha brindado la mujer que amo Luz Angélica Villaseñor Gómez, espero y siempre estemos juntos.

Espero no haber olvidado a nadie. Si existe alguien que no encuentre su nombre en esta lista me disculpo y lo invito a que escriba su nombre en el espacio libre que sigue a este parrafo.

# **Prefacio**

El contenido de esta tesis fue escrito como una referencia tanto como para ingenieros y técnicos involucrados en la fabricación de circuitos integrados en alta frecuencia, como para los nuevos estudiantes que incursionan en el tema. El objetivo de este trabajo es de proveer al lector de un completo entendimiento de todos los parámetros que gobiernan el comportamiento de un inductor integrado utilizado para operar en altas frecuencias (GHz.), desde lo más básico como lo es el concepto de inductancia hasta entender un proceso de fabricación de dichos inductores, el cual reduce las parásitas intrínsecas del mismo, dando como resultado un mejor desempeño del dispositivo.

En primera instancia se da una introducción a lo que es un inductor y todas las no idealidades que presenta, así como el uso de estos, en los diferentes circuitos que están presentes en un receptor o un transmisor. En el capítulo 1 se hace un estudio de las parásitas que existen en un inductor integrado sobre silicio, modelando estas con un programa desarrollado en Mathcad. El capítulo 2 contiene una revisión de algunos trabajos ya publicados, con el fin de recopilar datos y conocer los métodos ya utilizados para mejorar el desempeño de los dispositivos. El capítulo 3 contiene una reseña de los métodos necesarios para la fabricación de dichos dispositivos. Y por último el capitulo 4 describe el proceso de fabricación propuesto y un análisis mecánico de las causas por las cuales se puede presentar cierta cantidad de estrés y algunos métodos para reducirla.

## Introducción General

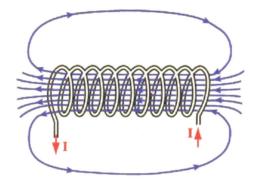

Para definir la *inductancia*, es necesario introducir el concepto de eslabonamiento de flujo. Considerar una espira de N vueltas como lo muestra la Fig. 0.1, en la cual una corriente I produce un flujo total Φ. Se supone que este flujo rodea cada una de las N vueltas, y que cada una de éstas eslabona el flujo total¹ El eslabonamiento de flujo NΦ se define como el producto del número de vueltas y el flujo que forma una vuelta. Para una espira que tiene una sola vuelta, el eslabonamiento de flujo es igual al flujo total. Ahora bien, la *inductancia* (llamada también *inductancia* propia) se define como la razón del total de eslabonamiento de flujo entre la corriente a la cual eslabonan [1]:

$$L = \frac{N\Phi}{I} \tag{1}$$

Esta definición se aplica solo para medios magnéticos lineales, es decir, solo para aquella situación en la que el flujo es proporcional a la corriente. Por otro lado, si están presentes los materiales ferromagnéticos en la región interna de las espiras, no existe una definición particular de inductancia que sea útil en todos los casos. En la práctica, los inductores son dispositivos diseñados para almacenar energía por medio de la presencia de campo magnético, esto se logra gracias a la forma en espiral que tiene su disposición y a los materiales que se usan en su construcción.

Fig. 0. 1 Inductor de espira circular. En su forma más simple, es un dispositivo de dos terminales formado por un alambre conductor embobinado.

La siguiente expresión es la formula de Wheeler, la cual es usada para calcular la inductancia en función del diámetro del alambre conductor D, del número de vueltas y de la longitud del embobinado  $\lambda$ .

$$L = \frac{0.001 * N^2 * D^2}{\lambda + 0.45 * D}$$

(2)

<sup>&</sup>lt;sup>1</sup> La unidad del flujo magnético es el Weber (Wb), así llamado por el físico alemán Wilhelm Weber (1804-1891).

Al emplear (2), la precisión alcanzada es del orden del 1% para bobinas cuya relación  $\lambda$ D>2/5 [2]. En la práctica es común usar hilo conductor de cobre para frecuencias de hasta 50 MHz. Mientras que para frecuencias superiores se usan conductores cobre-plata<sup>2</sup>.

La forma de representar esquemáticamente un inductor es la que se muestra en la Fig. 0.2, donde se ha omitido mostrar su convención corriente-voltaje. El símbolo representa un embobinado cuya región central es aire (denominado también sin núcleo), o bien una espira con dos líneas paralelas que representa un inductor con núcleo de algún material [2]. La razon por la cual se deben de diferenciar los inductores sin núcleo de los que sí lo tienen, es que el modelo matemático que da cuenta del principio básico de operación no es el mismo

Fig. 0. 2 Símbolos esquemáticos de inductores.

Desde el punto de vista eléctrico, en un inductor la presencia de una corriente eléctrica produce un campo magnético concentrado alrededor de él, este flujo de campo equivale a la energía almacenada y representa la energía cinética de los portadores de carga en el inductor. Entre más corriente fluya por el dispositivo mayor será el campo magnético, y más energía se almacenará. La habilidad de un inductor de almacenar energía en función de la corriente resulta en una tendencia a mantener un nivel de corriente constante; en otras palabras, el inductor se resiste a los cambios de corriente. Cuando es el caso, el inductor se resiste a tal cambio produciendo un voltaje opuesto a la polaridad de este [3].

Cuando se incrementa la corriente en un inductor, éste produce un voltaje opuesto a la dirección del flujo de la corriente, actuando como una carga. En esta condición se dice que el inductor se está *cargando*, debido a que hay un incremento de energía almacenada en su campo magnético. Por el contrario, cuando la corriente en el inductor disminuye, se produce un voltaje que concuerda con la dirección del flujo de corriente, entonces se dice que se está *descargando*, debido a que la energía almacenada disminuye. Esta energía, va al resto del circuito [3].

El flujo de campo magnético (y por lo tanto la energía almacenada) depende del material en que esté enrollado el embobinado. Estos dispositivos con núcleo de algún material ferromagnético (como el hierro) producen un flujo de campo más intenso que las que no lo tienen (por ejemplo núcleo de aire o aluminio son opciones alternativas) [4].

La Fig. 3a muestra un inductor con núcleo de aire mientras que la figura 3b muestra otro con núcleo de hierro. Como se puede ver, el último tiene una mayor concentración de campo. Esto se debe a que la propiedad ferromagnética del núcleo favorece la generación de un dominio magnético interno, dirigiendo las líneas de campo producidas por la corriente en el inductor. Esta característica tiene como consecuencia que el campo magnético se multiplique en factores de 10. A manera de ejemplo considerar los siguientes casos:

<sup>&</sup>lt;sup>2</sup> Como comentario, para aplicaciones de radiofrecuencia se utiliza el hilo de Liz. Es práctica común que el hilo conductor utilizado en la fabricación de inductores debe estar aislado con barniz especial o bien recubierto con un aislamiento plástico para evitar cortos circuito entre espiras.

Núcleo de aire: El embobinado (llamado también devanado) se realiza sobre un material no magnético (fibra, plástico, etc.). En los casos dónde no se utiliza soporte, el dispositivo queda conformado sólo por la rigidéz mecánica del conductor.

Núcleo de hierro: Considerando que su permeabilidad es mayor que la debida al aire (10 a 10<sup>2</sup>), aumenta el valor de la inductancia. Sin embargo, sólo se emplea en bajas frecuencias porque a frecuencias mayores las pérdidas son elevadas.

Núcleo de ferrita: Son óxidos de metales magnéticos, de alta permeabilidad (10 a 10<sup>4</sup>) que además son dieléctricos [11]. Existe una gran variedad en el mercado en función de la frecuencia de interés (ver la Tabla 1).

| Tipo de Material              | Descripción del Material                                                                                    |

|-------------------------------|-------------------------------------------------------------------------------------------------------------|

| MATERIAL 33 (μ = 850)         | Ferrita de magnesio de zinc, tiene baja resistividad y se utiliza en aplicaciones entre 1 KHz. y 1 MHz      |

| MATERIAL 43 ( $\mu$ = 850)    | Alta resistividad. Para inductores de mediana frecuencia.                                                   |

| MATERIAL 61 (μ = 125)         | Ofrece moderada estabilidad y altos valores de Q en rangos de 0.2 MHz. a 15 MHz.                            |

| MATERIAL 63 ( $\mu = 40$ )    | Inductores de Q alta, en rangos de 15 MHz a 25 MHz se puede reemplazar por el material 67.                  |

| MATERIAL 64 (μ = 250)         | Tiene excelente estabilidad a la temperatura y buen desempeño arriba de 400 MHz.                            |

| MATERIAL 67 ( $\mu$ = 40)     | Similar al material 63, tiene gran estabilidad a la temperatura.                                            |

| MATERIAL 68 ( $\mu = 20$ )    | Alta resistividad, y excelente estabilidad a la temperatura.<br>Altos valores de Q entre 80 MHz. y 180 MHz. |

| MATERIAL 73 ( $\mu = 2500$ )  | Tiene buenas propiedades de atenuación entre 1 MHz y 50 MHz.                                                |

| MATERIAL 77 ( $\mu = 2000$ )  | Se usa extensivamente en frecuencias de atenuación entre 0.5 MHz y 50 MHz.                                  |

| MATERIAL 'F' ( $\mu = 3000$ ) | Se usa extensivamente en frecuencias de atenuación entre 0.5 MHz y 50 MHz.                                  |

| MATERIAL K (μ = 290)          | Se usa en transformadores de líneas de transmisión.                                                         |

| MATERIAL W (μ= 10, 000)       | Alta permeabilidad se utiliza en bajas frecuencias, entre 100 KHz y 1 MHz.                                  |

| MATERIAL H ( $\mu$ = 15, 000) | Muy alta permeabilidad se utiliza para frecuencias por debajo de 200 KHz.                                   |

Tabla 0. 1 Algunos materiales utilizados en el núcleo de inductores [8].

Fig. 0. 3 Inductores con núcleo de aire y de hierro.

#### Características de la inductancia

Un mayor número de espiras producirá en el inductor un campo magnético más intenso [3]. Por ejemplo, la Fig. 0.4b representa un inductor cuyo campo es más intenso que el producido por su contraparte en (a). En esta representación se supone que, en ambos inductores, la corriente I y área de las espiras son de igual valor.

Fig. 0. 4 Inductores con diferente número de espiras.

El área de las espiras en un inductor también es un factor que influye en la intensidad del campo, de tal manera que si se tienen dos inductores, por los cuales circula cantidades idénticas de corriente y tienen igual número de espiras pero con diferente área, como se muestra en la Fig. 0.5, aquel que tenga mayor área presentará menor oposición al flujo de campo, por lo tanto, éste obtendrá una fuerza de campo de mayor intensidad.

Fig. 0. 5 Inductores con diferente área.

Otro factor que influye en la intensidad de campo, es la longitud del inductor, de la cual se puede decir, que una longitud más grande presenta mayor oposición a la formación de flujo de campo [3]. Como ejemplo, en la Fig. 0.6a, el inductor presenta mayor oposición a la formación de flujo que el representado por 0.6b.

Fig. 0. 6 Inductores con diferente longitud.

#### No idealidades del inductor

Inuductancia propia, e Inductancia mutua.

La auto inductancia es causada por la longitud efectiva, el ancho, y el grosor del conductor, mientras que la inductancia mutua es causada por el acoplamiento adyacente entre segmentos paralelos. Dependiendo de la dirección en que fluye la corriente en segmentos paralelos, la inductancia mutua es positiva si la corriente está en la misma dirección, y negativa si la corriente está en dirección opuesta [7].

#### **Dimensiones**

Además de hacer consideraciones para minimizar el circuito, la dimensión del inductor influye en el desempeño eléctrico<sup>3</sup> Se prefieren dispositivos pequeños y delgados debido a que dispositivos grandes requieren terminales de gran dimensión, lo cual trae como consecuencia un incremento en el valor de las capacitancias parásitas [5].

## Capacitancia Parásita.

Todos los inductores presentan ciertas características de capacitancia, ésta se deriva de la proximidad que hay entre las espiras del inductor, como lo muestra la Fig. 0.7 y depende de los materiales de la estructura. Estrictamente hablando, la situación extrema ocurre si su constante dieléctrica es de gran valor. Las terminales a las cuales el inductor es conectado, también son una fuente de capacitancia, donde ésta, inclusive puede ser mayor que la capacitancia parásita interna [5].

Fig. 0. 7 Inductor con sus capacitancias parásitas

El valor de inductancia depende también de su capacidad distribuida o parásita, la cual puede estimarse de la siguiente manera:

<sup>&</sup>lt;sup>3</sup> Altos valores de inductancia no son un factor importante en muchas de las aplicaciones de alta frecuencia. Típicamente el rango de interés es de 3 nH a 100 nH. Los factores críticos son estabilidad y tolerancia del inductor al operar en altas frecuencias [4].

<sup>&</sup>lt;sup>4</sup> Es crítico para los inductores trabajando en altas frecuencias, que la capacitancia parásita se disminuya.

$$C_{p} = KD (4)$$

donde D es el diámetro de la espira [mm], K depende de la relación  $\lambda$ /D de la bobina (ver Tabla 2) y  $C_p$  es la capacitancia parásita.

| $\lambda d$ | 0,1   | 0,3  | 0,5  | 0,8  | 1     | 2    | 4     | 6     | 8     | 10    | 15    | 20    | 30   |

|-------------|-------|------|------|------|-------|------|-------|-------|-------|-------|-------|-------|------|

| K           | 0,096 | 0,06 | 0,05 | 0,05 | 0,046 | 0,05 | 0,072 | 0,092 | 0,112 | 0,132 | 0,186 | 0,236 | 0,34 |

**Tabla 0. 2** Valores típicos de K dependiendo de la relación  $\lambda D$ .

Nótese que K presenta reducidos valores (y por lo tanto también se reduce  $C_p$ ) para una relación  $1 < \lambda/D < 2$ .

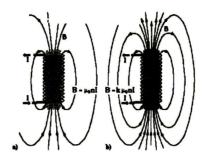

#### Resistencia.

Además de la inductancia y la capacitancia parásita, el inductor exhibe también el comportamiento de una resistencia. A bajas frecuencias, predomina la resistencia del conductor  $\mathbf{R}_{CD}$ , mientras que a muy altas frecuencias la resistividad del material conductor es más importante que  $\mathbf{R}_{CD}$  [5]. Lo anterior se debe al efecto *skin* (ver Fig. 0.8), es decir, la corriente no fluye completamente a través del área transversal del conductor, si no que fluye a través de las paredes del mismo, por eso, es importante que el material de la bobina sea de baja resistividad (plata, cobre, oro, aluminio) [5]. La Tabla 3 muestra la resistividad de algunos materiales [7].

| MATERIAL  | RESISTIVIDAD en (Ωm) |  |  |  |  |  |  |

|-----------|----------------------|--|--|--|--|--|--|

| METALES   |                      |  |  |  |  |  |  |

| Plata     | 1.59 e-8             |  |  |  |  |  |  |

| Cobre     | 1.67 e-8             |  |  |  |  |  |  |

| Oro       | 2.35 e-8             |  |  |  |  |  |  |

| Aluminio  | 2.66 e-8             |  |  |  |  |  |  |

| Wolframio | 5.65 e-8             |  |  |  |  |  |  |

| Niquel    | 6.84 e-8             |  |  |  |  |  |  |

| Hierro    | 9.71 e-8             |  |  |  |  |  |  |

| Platino   | 10.6 e-8             |  |  |  |  |  |  |

| Plomo     | 20.65 e-8            |  |  |  |  |  |  |

Tabla 0. 3 Resistividad de algunos materiales. ¿cuál es el más utilizado y por qué?

Fig. 0. 8 En (a) se muestra una corriente I circulando a través de un conductor a baja frecuencia, mientras que en (b) se ilustra el efecto skin en un conductor cuando la corriente fluye a muy alta frecuencia. c) y d) muestran un corte de sección transversal en la dirección x de a) y b) respectivamente.

### Frecuencia de Auto resonancia (SFR)

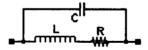

En esta frecuencia es de gran importancia tomar en cuenta las parásitas del inductor, ya que debido a ellas éste cambia su comportamiento. Si se analiza la Fig. 0.9 (circuito equivalente del inductor), la resistencia R está dada prácticamente por la resistencia óhmica del alambre, despreciándose la que implica pérdidas de calor por el núcleo ferromagnético, la capacitancia C es la parásita que existe entre las espiras individuales, y finalmente la inductancia L está dada por la geometría y núcleo del embobinado [6].

Calculando la impedancia del circuito equivalente, se obtiene:

$$Z = \frac{Ls + R}{LCs^2 + RCs + 1} \tag{6}$$

se puede apreciar que la impedancia presenta una resonancia en (LC). Graficando esta expresión, se obtiene una respuesta como la que muestra la figura 0.10, de la cual se puede ver que existe una frecuencia donde el inductor deja de comportarse como tal, para comportarse como un capacitor. A esta frecuencia se le denomina frecuencia de auto resonancia (SFR). En aplicaciones de alta frecuencia es importante reducir la capacitancia parásita tanto como sea posible, ya que la frecuencia de auto resonancia debe ser mayor a la frecuencia de operación de la aplicación.

Fig. 0. 9 Modelo equivalente del inductor.

Fig. 0. 10 Respuesta de frecuencia contra impedancia de un inductor real

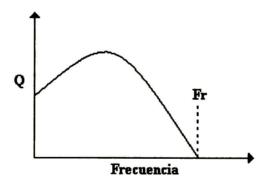

### Factor de Calidad (Q)

El factor Q es la razón de la impedancia reactiva a la resistencia equivalente en serie (ESR), es decir, es la razón de la potencia almacenada a la potencia disipada [5]. Si el inductor fuera fabricado con un conductor perfecto su Q sería infinita y no tendría pérdidas, pero no existe un conductor perfecto al alcance de cualquier persona, por lo tanto, un inductor siempre presentará una Q finita. A bajas frecuencia la Q de un inductor es alta pórque la única pérdida que presenta es la resistencia del conductor, que es relativamente pequeña, pero conforme la frecuencia aumenta, el efecto skin y la capacitancia parásita entre espiras tiende a degradar el factor de calidad. Esto se puede observar en la Fig. 0.11. A bajas frecuencias, Q es directamente proporcional a la frecuencia por lo que, para moderadas frecuencias, su reactancia se incrementa y el efecto skin todavía no se presenta. La parte semiplana de la curva se presenta cuando la resistencia en serie y la reactancia están cambiando a la misma razón. Después de estas frecuencias, la capacitancia parásita y el efecto skin se combinan y decrece el valor de Q hasta llegar a cero en su frecuencia de resonancia [10].

Algunos métodos para incrementar Q son los siguientes:

- 1.-Usar un diámetro más grande del cable. Esto disminuye la resistencia de las espiras.

- 2.-Separar las espiras con el fin de reducir la capacitancia parásita.

- 3.-Incrementar la permeabilidad del núcleo. Se obtiene colocando un material ferromagnético en el núcleo del inductor [10].

Fig. 0. 11 Variación de Q en un inductor vs. frecuencia.

#### Potencia Máxima

Para los inductores este parámetro es básicamente la máxima corriente que el inductor puede soportar sin que éste se sobrecaliente. Esta máxima potencia depende primordialmente de 3 factores: ESR, Conductividad térmica del material, y la máxima temperatura de operación permisible. La ESR determina la cantidad de potencia generada en el inductor bajo condiciones de altas corrientes; la conductividad térmica del material, y la máxima temperatura de operación permisible determinan la capacidad de que el dispositivo remueva el calor generado. La potencia máxima no es un parámetro de importancia en aplicaciones de alta frecuencia [5].

<sup>&</sup>lt;sup>5</sup> La inductancia efectiva se da por la existencia de capacitancias parásitas, y la propia dependencia a la frecuencia que tiene el inductor. Esto es, debido al efecto de la impedancia del dispositivo con respecto a la variación de frecuencia [4].

#### Importancia de los inductores.

La importancia de los inductores en el diseño de circuitos, se debe a las propiedades fisico-eléctricas que poseen los mismos, gracias a éstas, es posible manipular algunas señales eléctricas (filtros), y acoplar impedancias entre dos circuitos, lo anterior se logra debido al comportamiento variable que presenta su impedancia conforme varía la frecuencia. Por esto, los inductores son de gran importancia en el diseño de circuitos para aplicaciones de alta frecuencia. A continuación se muestran algunos ejemplos de circuitos que utilizan inductores en aplicaciones de RF.

Inductores en amplificadores de alta frecuencia.

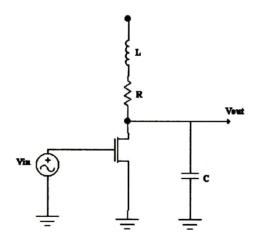

Antes de 1930, cuando la televisión empezaba a desarrollarse, un problema de suma importancia era el diseño de amplificadores con una respuesta máximamente plana a través de un ancho de bande de 4 Mhz. Aunque obtener este ancho de banda, actualmente parece trivial, era un reto con los dispositivos que se tenían en ese tiempo. Aún más, el amplificador debía de ser lo suficientemente barato para fabricarlo en masa; por lo tanto, el número de bulbos debería de ser mínimo. Una técnica que satisface estos requerimientos de grandes anchos de banda a bajo costo es la denominada shunt peaking, y fue utilizado en televisiones desde 1970. Un amplificador shunt-peaked es mostrado en la Fig. 0.12, es básicamente un amplificador en configuración fuente común con la incorporación de un inductor [12].

Fig. 0. 12 Amplificador Shunt-Peaked. La capacitancia C representa la carga en el nodo de salida; la resistencia R es la carga efectiva y el inductor L provee el incremento del ancho de banda.

Se supone que en un transistor ideal los únicos elementos que controlan el ancho de banda son R, C, y L. Por lo tanto, se puede utilizar el modelo de pequeña señal mostrado en la Fig 0.13. Es claro que la función de transferencia  $V_{out}$  /  $i_{in}$  es la impedancia de la red RLC, esto muestra que se puede analizar de manera directa.

Fig. 0. 13 Modelo en pequeña señal del amplificador Shunt-Peaked.

En principio, se sabe que la ganancia puramente resistiva del amplificador fuente común es proporcional a  $g_m R_L$ , donde  $g_{mn}$  es la transconductancia del transistor y  $R_L$  es la resistencia de carga. Cuando se incluye una carga capacitiva, la ganancia eventualmente cae conforme la frecuencia de operación aumenta, debido a que la impedancia del capacitor disminuye. Incorporando una inductancia en serie con el resistor de carga provee una componente extra en la impedancia, la cual incrementa su valor conforme se aumenta la frecuencia esto es, se introduce un cero que ayuda a que el ancho de banda aumente.

#### Inductores en LNA's.

En la actualidad, motivados por el crecimiento del mercado de los sistemas de comunicación de radio frecuencia (RF), se ha dedicado mucho esfuerzo a la implementación de componentes de RF en tecnología CMOS. El amplificador de bajo ruido es el bloque más demandado en un sistema de RF. La especificación de bajo ruido se debe satisfacer simultáneamente con un factor de calidad alto, ganancia de potencia, un buen acoplamiento de impedancia, buena linealidad, bajo consumo de potencia, y bajo costo. Como ya se sabe, la segunda etapa de un receptor típico, después de un filtro de RF es un amplificador de bajo ruido (LNA) Fig. 0.14; el cual, su función principal es la de proveer suficiente ganancia para que se pueda despreciar el ruido que se transmite a las siguientes etapas; además de proveer una ganancia, frecuentemente debe presentar una impedancia específica de  $50 \Omega$ , a la entrada de la fuente [13].

Fig. 0. 14 Bloque básico de un receptor.

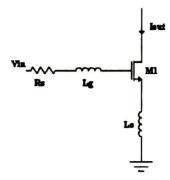

Un método para lograr esto último es emplear una degeneración inductiva de fuente. Una importante ventaja de este método, es que se tiene control de la parte real de la impedancia al escoger el valor de inductancia, ver la Fig. 0.15. En el circuito de esta figura,  $L_s$  se selecciona para proveer la impedancia de entrada deseada .Como ésta originalmente tiene entrada puramente resistiva en resonancia, requiere otro grado de libertad, que es provisto por la inductancia  $L_g$  [12].

Fig. 0. 15 LNA de banda angosta con degeneración inductiva en la fuente.

### Amplificadores sintonizados

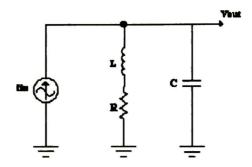

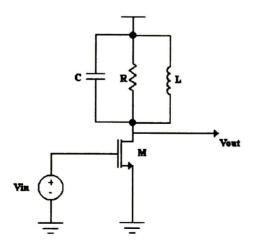

Frecuentemente no es necesario tener amplificadores de banda ancha, sino que se requiere sólo amplificación en un rango angosto de frecuencias. Los amplificadores sintonizados son ámpliamente utilizados en circuitos de comunicaciones para proveer amplificación de las señales deseadas y un grado de filtrado de las señales no deseadas. Un ejemplo es el amplificador de fuente común con sintonización de carga, el cual se muestra en la Fig. 0.16. Si se supone una impedancia de la fuente igual a cero y si se desprecia la resistencia de compuerta, entonces la capacitancia de drenaje a compuerta  $C_{\rm gd}$  puede ser dominada por la capacitancia C. En dicho caso, se puede modelar el circuito como un paralelo RLC. A bajas frecuencias, el inductor se encuentra en corto-circuito y la ganancia es cero, mientras que a altas frecuencias la ganancia es cero pórque el capacitor se encuentra en corto-circuito. A la frecuencia de resonancia del circuito RLC, la ganancia es simplemente  $g_m R$ , debido a que a dicha frecuencia el capacitor y el inductor se eliminan [12].

Fig. 0. 16 Amplificador de fuente común con sintonizador de carga.

### Requerimientos de un inductor

Para diseñar un inductor se deben de tomar en cuenta todas la consideraciones que cumplan con los requerimientos de diseño; es decir, se debe de tener un listado de especificaciones como el que se muestra en la Tabla 3 así se asegura que el dispositivo se desempeñe correctamente en la aplicación.

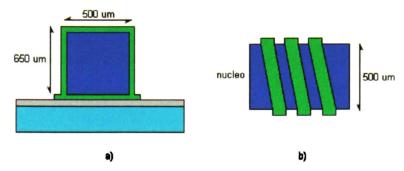

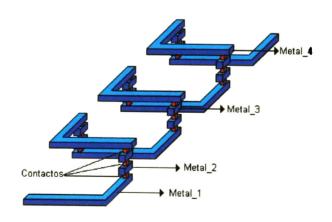

Con el incremento en la frecuencia de operación de los circuitos y la miniaturización de los sistemas portátiles, hoy en día, se ha tenido la necesidad de diseñar inductores pequeños y de alta calidad. Estos, son generalmente utilizados en amplificadores y osciladores como parte de un circuito LC diseñado para sintonizar éstos a una frecuencia deseada. Organizados por sus características físicas y eléctricas, los microinductores se pueden clasificar en dos categorías: inductores externos, e integrados, en donde los últimos se pueden subdividir en inductores activos<sup>6</sup>, pasivos planares, y pasivos tridimensionales. Los inductores activos provienen de emular el comportamiento de un inductor con ciertas configuraciones de transistores, los inductores pasivos planares, como su propio nombre lo dice son espiras de algún metal que se encuentran en un solo plano, y los inductores pasivos tridimensionales, son bobinas que se hacen con la unión de diferentes metales, en diferentes planos, la Fig. 0.17 muestra un ejemplo de cada uno de ellos. En las siguientes subsecciones se hará una revisión de estos inductores en detalle.

| Nº | Especificaciones.                                                    |

|----|----------------------------------------------------------------------|

| 1  | Inductancia y tolerancia aceptable.                                  |

| 2  | Aplicación.                                                          |

| 3  | Dimensiones máximas o el espacio disponible para el inductor.        |

| 4  | Requerimientos de montaje.                                           |

| 5  | Especificar si se requiere para un diseño de hardware en particular. |

| 6  | Promedio máximo de corriente directa que fluirá a través de él.      |

| 7  | Máximo pico que corriente.                                           |

| 8  | Tipo de señal alterna que se va a manejar.                           |

| 9  | Gráfica con el mínimo de impedancia requerido contra frecuencia.     |

| 10 | Máximo voltaje de trabajo entre terminales.                          |

| 11 | > Si se va trabajar con voltajes en a.c. especificar la frecuencia   |

Tabla 0. 4 Especificaciones de diseño.

<sup>&</sup>lt;sup>6</sup> El estudio de emular inductancias usando elementos activos, empezó cerca de 1960. La idea era, utilizando un transistor y algunas técnicas de realimentación, generar en dicho circuito una salida inductiva.

Fig. 0. 17 a) Inductor activo [5], b) Inductor pasivo planar cuadrado [6], c) Inductor de espira multi-capa [7].

Los inductores externos (bondwire), permiten lograr un alto factor de calidad pero no tienen buen comportamiento cuando se trabajan en altas frecuencias. Por otra parte, los inductores planares manejan Q's limitadas pero tienen inductancias que están bien definidas en un amplio rango de frecuencias (altas frecuencia). Por esto, los inductores planares se han convertido en elementos esenciales de bloques para circuitos de comunicación como Osciladores Controlados por Voltaje (VCO's), Amplificadores de Bajo Ruido (LNA's), Mezcladores, Filtros de Frecuencia Intermedia (IFF), etc. La razón es simple, el mayor valor agregado está en el diseño y desarrollo de sistemas portátiles de alto desempeño. Sin embargo, aún cuando hay un mercado potencial de nuevos productos, el desarrollo de inductores completamente integrados en materiales semiconductores de bajo costo (por ejemplo silicio) constituye hoy en día un enorme campo de investigación. En esta se pretende lograr dos propósitos: Por un lado desarrollar inductores compatibles con tecnología CMOS y, por el otro, incrementar el valor de Q, ya que los reducidos valores obtenidos en la actualidad han detenido la producción en masa de sistemas de RF completamente integrados.

Por lo anterior, y considerando la utilidad de inductores para el desarrollo de sistemas de RF, el objetivo de este trabajo de tesis es proponer un proceso de fabricación, compatible con tecnologías CMOS, que permita construir inductores planares sobre un substrato semiconductor (silicio). Por otro lado, si bien es cierto que este tipo de diseños ya han sido reportados, también es cierto que para incrementar el factor de calidad Q se han reportado inductores flotantes fabricados mediante técnicas de micromaquinado. Por lo tanto, en este trabajo no sólo se presentan las consideraciones de diseño de esta clase de inductores, sino que además se desarrollará un proceso de fabricación que minimice el uso de pasos de fotolitografía y/o reduzca el número de películas depositadas. Finalmente el desarrollo de inductores flotantes presentados en este trabajo estará orientado a aplicaciones para rango de 800 MHz. a 5 GHz.

#### Referencias.

- [1] William H. Hayt, JR. "Teoría Electromagnética" Quinta Edición Mc Graw Hill 1996.

- [2] Página Web "http://www.ing.unp.edu.ar/labelectronica/asignaturas/ TC1/tutoriales/inductores/desarrollo.htm

- [3] Tony Kuphaldt, "Lessons in Electric Circuits" Quinta Edición, Volumen 1-DC

- [4] Página Web "http://hyperphysics.phy-astr.gsu.edu/hbase/magnetic/elemag.html#c5"

- [5] Barry Breen "Multi-Layer Inductor for High Frecuency" A Kyocera Group Company

- [6] Página Web "http://www.personal.u-net.com/%7Ehills2/electron/induct.htm"

- [7] Stefan Staff "Printed Inductors In RF Consumer Aplications"

- [8] Página Web "http://sausalito.valpo.plaza.cl/ci/ciencias/fisica/mod3/f3m2a008.htm"

- [9] Página Web "http://www.bytemark.com/products/ferrmat.htm (Ferrite Materials.htm)"

- [10] Chris Bowick "RF Circuit Design" Primera Edición, Library of congress catalog-in publication data.

- [11] Página Web "http://www.ing.unp.edu.ar/labelelectronica/asignaturas/TC1/tutoriales/inductores/desarrollo.htm"

- [12] Thomas H. Lee "The design of CMOS Radio-Frecuency integrated circuit" Primera edición, Cambridge University Press, 1998.

- [13] Khaled Sharaf "2 V, 1-GHz CMOS Inductorless LNAs with 2-3 dB NF" IEEE, The 12<sup>th</sup> International Conference Microelectronics, Teheran, Oct, 31-Nov. 2,2000 pp. 379-383

# Capitulo 1

## Inductores Completamente Integrados en Silicio

Los circuitos de radio frecuencia (RF) de hoy en día están compuestos por un gran número de componentes pasivos (inductores, capacitores y resistores). De aquí que el diseño de éstos depende ampliamente del buen entendimiento que tenga el diseñador de las características eléctricas de cada uno de ellos. En tecnologías modernas de circuitos integrados en silicio, es práctica común el desarrollo de elementos resistivos y capacitivos; sin embargo, debido a la miniaturización de los sistemas, estas tecnologías están desarrollando inductores a partir del uso de los materiales propios del proceso de fabricación. Este hecho tiene varias implicaciones y, por tal razón, este capitulo muestra, en primera instancia, el modelado de un inductor pasivo integrado, incluyendo todas las no idealidades que ello implica.

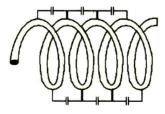

Debido a las muchas desventajas que tienen los inductores activos con respecto a los pasivos (consumo de potencia, mayor ruido, ancho de banda limitado, etc.), es necesario la integración de inductores pasivos con el fin de disminuir el consumo de potencia y todas aquellas fuentes de ruido. Por la naturaleza de las tecnologías de fabricación, el desarrollo de elementos pasivos es del tipo planar. Por lo tanto, las formas geométricas de espiras más populares son: cuadrada, hexagonal, octagonal, y circular. De todas ellas la más adecuada para aplicaciones de RF es la espira circular, sin embargo, no todos los procesos de fabricación tienen la capacidad de transferir patrones circulares, por lo que se opta por aquellos basados en ángulos rectos. La Fig. 1.1 muestra las diversas opciones para el diseño de espiras planares.

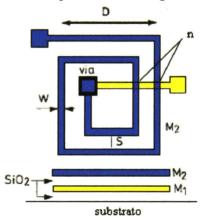

Fig. 1. 1 a) Cuadrada, b) Hexagonal, c) Octagonal, d) Circular. Tradicionalmente el material usado es aluminio, el cual es aislado del material semiconductor mediante una película de óxido de silicio de muy alta calidad (SiO<sub>2</sub> térmico).

### 1.1 Características de inductores integrados.

El valor de la inductancia en un inductor integrado depende de su geometría, y puede ser descrita por dos componentes: la auto inductancia Ls, y la inductancia mutua M. La primera es causada por la longitud efectiva, el ancho, y el grosor del conductor, mientras que la última es debida a los segmentos paralelos adyacentes. Esta inductancia total puede ser calculada resolviendo las ecuaciones de Maxwell. Una solución numérica se puede obtener usando un simulador tridimensional (3-D) de elemento finito, como MagNet. Sin embargo, estos simuladores requieren grandes tiempos de cómputo, por lo que no son apropiados para el diseño de inductores si no más bien son útiles para la verificación del diseño.

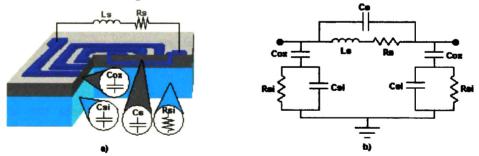

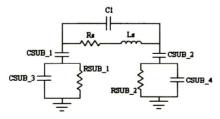

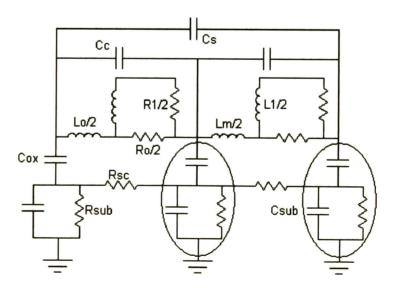

Además de la inductancia, es necesario tener en cuenta todos los elementos parásitos que se presentan inherentemente al integrar un inductor pasivo, como los son: la resistencia en serie R<sub>s</sub>, la cual toma en cuenta la profundidad del efecto piel <sup>7</sup> del conductor así como la distribución de corriente en el conductor. El substrato es otro problema en este diseño. En tecnologías de silicio, el substrato, la espira y el dieléctrico forman entre ellos un capacitor que entra en resonancia con el inductor. A cierta frecuencia este circuito LC representa la máxima frecuencia útil de operación del inductor, la cual puede aparecer dentro del rango de frecuencias de interés si es que no se tomó en consideración tal característica durante su diseño. La proximidad del substrato también degrada el factor de calidad Q debido a las pérdidas en el substrato. Una efecto parásito adicional es la capacitancia C<sub>s</sub> que se forma entre la espira y la pista metálica que sirve de conexión con el nodo centro ubicado en el centro geométrico de la espira. La Fig. 1.2a muestra un corte del inductor integrado, así como cada una de los efectos parásitos que se encuentran en él, mientras que la Fig. 2b muestra el circuito eléctrico equivalente.

Fig. 1. 2 capacitancia en serie  $C_a$ , capacitancia del oxido  $C_{ox}$ ,  $C_{ai}$  y  $R_{ai}$  representan la capacitancia y la resistencia del substrato,  $R_a$  resistencia en serie, y  $L_a$  Inductancia.

## 1.2 Cálculo de los efectos parásitas

Un estimado de la resistencia en serie se puede obtener a partir del siguiente modelo [1].

$$Rs = \frac{\rho^* \lambda}{w^* \delta^* \left(1 - e^{\frac{1}{\delta}}\right)}$$

(1.1)

<sup>&</sup>lt;sup>7</sup> La distancia que la señal debe viajar en un medio con perdidas para reducir su valor a  $e^{-1} = 0.368 = 36.8$  % se le denomina profundidad de piel.

donde  $\rho$  es la resistividad del material,  $\lambda$  la longitud de la espira, w el ancho de la línea, t el grosor de la pista metálica, y  $\delta$  es la profundidad del efecto piel del metal. Este último está dado por

$$\delta = \sqrt{\frac{\rho}{\pi \mu_0 f}} \tag{1.2}$$

donde f es la frecuencia de operación. Por otro lado, la capacitancia C<sub>s</sub> se puede obtener de la siguiente expresión [1].

$$C_{s} = n * w^{2} \left[ \frac{\varepsilon_{ox}}{t_{oxM}} \right]$$

(1.3)

donde n es el número de cruces entre la espira y la pista conductora al punto central,  $\epsilon_{ox}$  es la constante dieléctrica del óxido de silicio  $t_{oxM}$  es el grosor del oxido entre las pistas conductoras.

La capacitancia  $C_{ox}$  se encuentra entre la espira y el substrato y se aproxima mediante una simple formula de capacitores de placas paralelas

$$Cox = \frac{1}{2} * \lambda * w * \frac{\varepsilon_{ox}}{t_{ox}}$$

(1.4)

donde  $t_{ox}$  es el grosor del óxido. En la práctica esta diferencia de óxidos no es muy relevante, es decir, estos dos óxidos pueden ser del mismo grosor, debido a que la diferencia de área que se forma entre los metales es mucho menor que la que hay entre la espira y el substrato, debido a esto se considera que la capacitancia entre metales es mucho menor que la formada entre la espira y el substrato.

Las pérdidas por substrato son modeladas con  $R_{si}$ , la cual toma en cuenta dos mecanismos diferentes: el primero es la corriente que fluye en el substrato hacia  $C_{ox}$ , y el segundo son las corrientes de imagen inducidas en el substrato por aquellas que fluyen en la espira [1]:

$$R_{si} = \frac{2}{\lambda * w * G_{sub}} \tag{1.5}$$

donde G<sub>sub</sub> es la conductancia del substrato por unidad de área, típicamente 10<sup>-7</sup> S/μm². Esta parásita, además de contribuir con pérdidas, las corrientes de imagen fluyen en dirección opuesta a las corrientes del inductor. De aquí que el efecto de imagen es cancelar parcialmente la inductancia. Este efecto indeseable viene asociado con otro más; conforme la temperatura aumenta la resistividad del substrato también se incrementa, entonces se reduce la cancelación y trae como consecuencia que la inductancia aumente con la temperatura. Se dice que este efecto es indeseable pórque si no se tiene un control de la temperatura a la que se está operando, tampoco se tendrá un control de la inductancia lo cual puede afectar el desempeño del circuito. En contraparte, si se tiene control de la temperatura puede ser benéfico al momento de realizar el diseño. Cuando se habla de control de temperatura se toma en cuenta tanto la temperatura del ambiente que lo rodea como la causada por

la corriente que fluye a través de él. La capacitancia parásita  $C_{si}$  es la capacitancia de substrato y viene dada por:

$$C_{si} = \frac{1}{2} * \lambda * w * C_{sub}$$

(1.6)

donde  $C_{sub}$  es la capacitancia del substrato por unidad de área [1]. La Fig. 1.3 muestra una espira con cada una de los parámetros necesarios para calcular sus parásitas.

Fig. 1. 3 Parámetros típicos de una espira conductora.

La eficiencia de un inductor, como ya se dijo en el capitulo anterior, se mide por su factor de calidad Q, el cual está limitado por efectos parásitos. La energía almacenada y los mecanismos de pérdida en un inductor fabricado en silicio pueden ser descritos por el modelo equivalente que se muestra en la Fig. 1.2b, donde L<sub>s</sub>, R<sub>s</sub>, R<sub>si</sub>, C<sub>si</sub>, C<sub>s</sub> y C<sub>ox</sub> representan la inductancia total, las pérdidas del conductor, pérdidas por substrato, la capacitancia del substrato, la capacitancia entre espiras y la capacitancia de óxido, respectivamente.

Para un inductor, sólo es de interés la energía de campo magnético almacenado, cualquier energía de campo eléctrico almacenado debido a sus capacitancias parásitas se considera una pérdida. De aquí que Q es proporcional a la energía magnética almacenada, que es igual a la diferencia entre el pico de energía magnética menos el pico de energía eléctrica. Se dice que un inductor se encuentra en auto resonancia, cuando el pico magnético y eléctrico son iguales. Por lo que se puede decir que en ese momento Q es cero:

$$Q = 2\pi \frac{|\text{Pico de Energía Magnética - Pico de Energía eléctrica}|}{\text{Energía perdida en un ciclo}}$$

(1.7)

$$Q = \frac{\omega L_{s}}{R_{s}} * \frac{R_{p}}{R_{p} + \left[ \left( \frac{\omega L_{s}}{R_{s}} \right)^{2} + 1 \right] * R_{s}} * \left( 1 - \frac{R_{s}^{2} C_{0}}{L_{s}} - \omega^{2} L_{s} C_{0} \right)$$

(1.8)

En esta expresión, de izquierda a derecha, el primer factor representa la energía magnética almacenada y las pérdidas ohmicas en la espira; el segundo se debe al factor de perdidas del substrato representando la energía disipada en el substrato semiconductor, y el último factor es el término de auto resonancia.

En (1.8) se pueden observar algunos términos no descritos anteriormente, como lo son  $R_p$ , y  $C_o$ , éstos son los efectos combinados de las parásitas  $C_{ox}$ ,  $C_{si}$ , y  $R_{si}$ , y se pueden expresar de la siguiente manera:

$$R_{p} = \frac{1}{(2 * \pi * f)^{2} C_{ox} R_{si}} + \frac{R_{si} (C_{ox} + C_{si})^{2}}{C_{m}^{2}}$$

(1.9)

$$C_0 = C_p + C_s \tag{1.10}$$

donde

$$C_{p} = C_{ox} * \frac{1 + (2 * \pi * f)^{2} (C_{ox} + C_{si}) C_{si} R_{si}^{2}}{1 + (2 * \pi * f)^{2} (C_{ox} + C_{si})^{2} R_{si}^{2}}$$

(1.11)

#### 1.3 Cálculo del valor de inductancia

Para el cálculo de la inductancia total de la espira existen varios métodos, pero el más popular es el método de Greenhouse [2]. El cual básicamente calcula la inductancia de una espira cuadrada dividiéndola en secciones de conductores rectos, obteniendo con ésto su auto inductancia y sumándola para obtener el total. Además de la consideración de auto inductancia de cada conductor recto, se debe calcular la inductancia mutua (positiva o negativa) de los segmentos paralelos, para obtener la inductancia total de la espira.

La auto inductancia L<sub>0</sub> de un conductor recto está dada por:

$$L_0 = 0.0002\lambda \left[ \ln \left( \frac{2\lambda}{GMD} \right) - 1.25 + \frac{AMD}{\lambda} + \left( \frac{\mu}{4} \right) T \right]$$

(1.12)

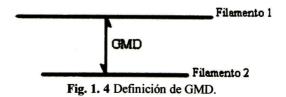

GMD y AMD representan la distancia media geométrica y media aritmética de la sección transversal del conductor,  $\mu$  es la permeabilidad del conductor y T es un parámetro de corrección de frecuencia. La distancia media geométrica GMD es la distancia entre dos filamentos imaginarios infinitamente delgados, donde su inductancia mutua es igual a la inductancia mutua entre los dos conductores originales (ver Fig 1.4). A su vez, la distancia media aritmética AMD es el promedio de todas las distancias que hay entre los puntos de un conductor y los puntos del otro.

Si se usa la capa superior de metal para definir la espira, la ecuación (1.12) se puede expresar como

$$L_{0} = 0.002\lambda \left[ \ln \left( \frac{2\lambda}{a+b} \right) + 0.5 + \frac{a+b}{3\lambda} \right]$$

(1.13)

donde a, b son las dimensiones rectangulares de sección transversal. En el caso de una espira rectangular, existen segmentos de conductor paralelos a otros, y la inductancia mutua de estos tramos paralelos contribuyen con la inductancia total del inductor.

La inductancia mutua de dos conductores paralelos está en función de la longitud de los conductores y de la distancia geométrica entre ellos:

$$M = 2 * \lambda * P \tag{1.14}$$

$$P = \ln \left[ \frac{1}{GMD} + \sqrt{1 + \frac{\lambda^2}{GMD^2}} \right] - \sqrt{1 + \frac{GMD^2}{\lambda^2}} + \frac{GMD}{\lambda}$$

(1.15)

$$\ln(GMD) = \ln(d) - \left[ \frac{1}{12\left(\frac{d}{w}\right)^2} + \frac{1}{60\left(\frac{d}{w}\right)^4} + \frac{1}{168\left(\frac{d}{w}\right)^6} + \frac{1}{360\left(\frac{d}{w}\right)^8} + \frac{1}{660\left(\frac{d}{w}\right)^{10}} \dots \right]$$

(1.16)

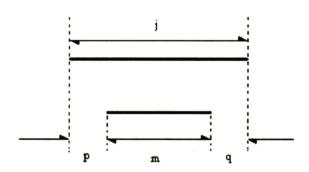

donde M es la inductancia mutua y P es el parámetro de inductancia mutua, d es la separación entre centros de los conductores. Para los conductores paralelos que se muestran en la Fig. 1.5, la inductancia mutua total se puede representar por

$$2M_{i,m} = (M_{m+p} + M_{m+q}) - (M_p + M_q)$$

(1.17)

Las inductancias mutuas individuales se calculan utilizando (1.14) y las de  $\{m+p\}$  y  $\{m+q\}$  se calculan con la siguiente formula

$$M_{m+p} = 2\zeta_{m+p}P_{m+p} = 2(m+p)P_{m+p}$$

(1.18)

De lo anterior se concluye que, la inductancia mutua total es la sumatoria de las inductancias mutuas de cada segmento paralelo de conductor.

$$L_{T} = L_{0} + M_{+} + M_{-} \tag{1.19}$$

donde  $L_T$  es la inductancia total de la espira,  $L_0$  es la suma de las auto inductancias de los segmentos rectos,  $M_+$  es la suma de las inductancias mutuas positivas, y  $M_-$  es la suma de las inductancias mutuas negativas.

#### 1.4 Resultados de los cálculos.

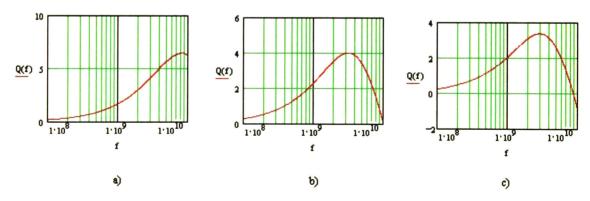

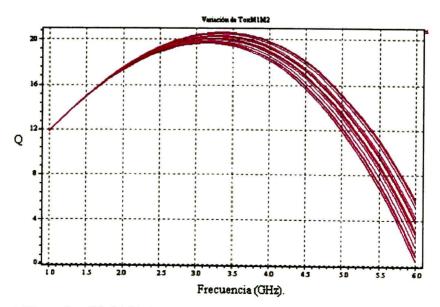

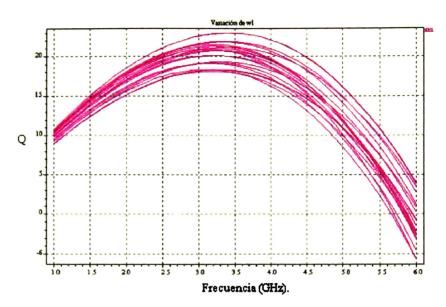

Con el modelo mencionado, se realizaron cálculos en Mathcad, y se obtuvo los resultados mostrados en las Tabla 1.1, 1.2 y 1.3 así como las gráficas dadas en la Fig. 1.6, 1.7 y 1.8

| t (µm) | s (µm) | W (µm) | λ (μm) | N | L (nH) |

|--------|--------|--------|--------|---|--------|

| 1      | 4      | 6      | 2000   | 3 | 3.73   |

| 1      | 4      | 6      | 4000   | 7 | 10     |

| 1      | 4      | 6      | 5000   | 9 | 10.54  |

Tabla 1. 1 Resultados de los cálculos con el método de Greenhouse variando N.

Fig. 1. 5 Conductores paralelos de una espira.

Fig. 1. 6 Gráficas de Q contra frecuencia a) N=3, b) N=7, c) N=9.

| t (µm) | s (µm) | W (µm) | λ (μm) | N | L (nH) |

|--------|--------|--------|--------|---|--------|

| 1      | 4      | 6      | 4000   | 7 | 10     |

| 1      | 8      | 6      | 4000   | 7 | 5.9    |

| 1      | 10     | 6      | 4000   | 7 | 4.4    |

Tabla 1. 2 Resultados de los cálculos con el método de Greenhouse variando s.

Fig. 1. 7 Gráficas de Q contra frecuencia a) s =4  $\mu m$  , b) s =8  $\mu m$ , c) s =10  $\mu m$ .

| t (µm) | s (µm) | W (µm) | λ (μm) | N | L (nH) |

|--------|--------|--------|--------|---|--------|

| 1      | 4      | 3      | 4000   | 7 | 14.7   |

| 1      | 4      | 6      | 4000   | 7 | 10     |

| 1      | 4      | 9      | 4000   | 7 | 6.5    |

Tabla 1. 3 Resultados de los cálculos con el método de Greenhouse variando w

Fig. 1. 8 Gráficas de Q contra frecuencia a) w = 3  $\mu$ m, b) w = 6  $\mu$ m, c) w = 9  $\mu$ m.

De la tabla 1.1 y la Fig. 1.6 se puede decir que al aumentar el número de vueltas manteniendo los demás parámetros constantes, se obtiene un aumento en el valor de inductancia asociada; pero el factor de calidad es afectado; es decir, éste se reduce. Por el contrario, si se aumenta la distancia que hay entre las pistas (tabla 1.2, Fig. 1.7) se experimenta un ligero aumento en el factor de calidad pero se presenta una disminución en el valor de la inductancia. El mismo resultado se experimenta si se aumenta el ancho de la pista (tabla 1.3, Fig. 1.8).

### Referencias.

- [1] C. Patrick Yue, Changsup Ryu, Jack Lau\*, Thomas H. Lee, and S. Simon Wong "a physical model for planar spiral inductors on silicon" Center for Integrated Systems", Stanford University, Stanford, CA 94305 \*Dept. of Electrical and Electronic Eng., The Hong Kong University of Science & Technology, in IEDM Tech. Dig., Dec. 1996, pp. 155–158.

- [2] H. Greenhouse, "Design of planar rectangular microelectronic inductors," IEEE Trans. PHP, vol. 10, no.2, pp. 101-109, June 1974.

# Capitulo 2

## Revisión de Trabajos Existentes

Basados en la necesidad de modelar y diseñar dispositivos a pequeña escala, apareció un nuevo campo tecnológico llamado miniaturización de sistemas, el cual se convirtió en parte del llamado, Sistemas Micro Electro Mecánicos (MEMS). En este electrónica y componentes mecánicos son miniaturizados e integrados. En particular el número de dispositivos electrónicos en un semiconductor ha crecido de 10 en 1960 a mas de un billón en los 90's. El éxito obtenido en estos dispositivos trajo, como motivación, pasar de técnicas de fabricación de circuitos integrados bidimensionales a técnicas tridimensionales. Existen diversas técnicas para la fabricación de MEMS, entre ellas están el micro maquinado de substrato, el de superficie, LIGA (Lithographie Galvanik Abformung, o litografía de rayos-X, electro deposición, y modelado) y LIGA utilizando litografía ultravioleta (UV) para realizar estructuras tridimensionales. Algunos de estos avances se pueden traducir en reducción de costos, en una significante reducción de área, y en estructuras más sofisticadas.

Utilizando materiales y técnicas de fabricación compatibles, estructuras tanto eléctricas, mecánicas, u ópticas pueden ser integradas monolíticamente con circuitería electrónica, obteniendo sistemas completos con más funciones. Estas tecnologías MEMS han sido usadas para mejorar el desempeño de muchos dispositivos sobre su contraparte convencional, como los son: sensores de presión, micro óptica, y radio frecuencia (RF).

El rápido avance que han tenido las comunicaciones, en aplicaciones militares, de aviación, de navegación, de sistemas de posicionamiento global (GPS), así como las comunicaciones personales (teléfonos celulares, computación inalámbrica, etc.) ha traído como consecuencia la necesidad de incrementar las comunicaciones inalámbricas. Una de muchas soluciones, es incrementar las frecuencias de operación de los dispositivos de comunicación. Otra solución es utilizar técnicas de modulación de alta velocidad, o mejorar la eficiencia de los dispositivos de RF a altas frecuencias. Múltiples transmisores y receptores operando simultáneamente en un mismo sitio requieren de una transmisión selectiva de altas frecuencias, un amplio rango dinámico de recepción (habilidad de recibir y manjar señales fuertes y débiles sobre un amplio rango de frecuencias), y filtrado tanto en el receptor como en el transmisor para asegurar la no interferencia de uno con el otro.

Como la tecnología típica de circuitos integrados CMOS, no ofrece el alto desempeño necesario en elementos de RF, se ha empezado a integrar MEMS para mejorar los circuitos integrados trabajando en altas frecuencias. Estos dispositivos, incluyen resonadores mecánicos y filtros, sintonizadores de frecuencia usando MEMS basadas en elementos pasivos como capacitores sintonizables e inductores con alto factor de calidad.

#### 2.1 Silicio como material base de RF.

A primera vista, las propiedades del Silicio parecen razonables para su uso como un substrato de RF. La constante dieléctrica es alta y no varía significativamente con respecto a la frecuencia y la temperatura, la conductividad térmica es tres veces mayor que la del GaAs, y la suavidad de la superficie es buena. La máxima resistividad práctica de crecimiento Czochralski en Silicio, sin embargo, es solo de  $10~\Omega$ -cm lo cual es algunos órdenes de magnitud menor que la del GaAs. A frecuencias mayores a 1~GHz la profundidad de piel (skin depth) para Silicio excede el grosor típico del substrato y entonces las pérdidas en RF se extienden sobre el substrato entero.

El rango típico de interés de frecuencias para las comunicaciones inalámbricas es de  $(1-10~{\rm GHz})$  donde típicamente el substrato es GaAs. Este material tiene muchas ventajas con respecto al Si: Menos pérdidas por substrato debido a su alta resistividad, al igual que el zafiro y el  ${\rm Al}_2{\rm O}_3$ ; además su movilidad de electrones es 6 veces mayor que la del Si. Sin embargo, los modernos procesos pueden proveer dispositivos activos con características de 0.1  $\mu$ m de longitud de canal. Estos dispositivos presentan frecuencias de corte de hasta 20 GHz lo cual sitúa al silicio en la posibilidad de ser utilizado en el rango de altas frecuencias. La tabla 1 muestra algunas propiedades de los materiales mencionados anteriormente.

|           | Permitividad Relativa | Resistividad<br>Ω-cm             | Conductividad Térmica<br>W/(cmk) |

|-----------|-----------------------|----------------------------------|----------------------------------|

| GaAs      | 12.9                  | 10 <sup>7</sup> -10 <sup>9</sup> | 0.46                             |

| Si        | 11.9                  | $10^2 - 10^3$                    | 1.45                             |

| Zafiro    | 11.9                  | >104                             | 0.42                             |

| $Al_2O_3$ | 9.8                   | $10^{11} - 10^{14}$              | 0.37                             |

Tabla 2. 1 Propiedades físicas de algunos materiales.

Desde luego que realizar un circuito completamente integrado requiere, no solo de dispositivos activos, sino que también de pasivos como son los inductores y los capacitores. Los inductores, en particular, son más críticos, por que el hecho de realizar una espira de metal sobre un substrato de Silicio presenta una alta degradación en el factor de calidad. Esta es causada por sus pérdidas tanto en el metal como en el substrato.