xx(178687.1)

### Centro de Investigación y de Estudios Avanzados del I.P.N. Unidad Guadalajara

# Diseño de un amplificador de potencia clase-E usando un transistor N-MOS de alto voltaje en una tecnología CMOS estándar

COORDINACIÓN GENERAL DE SERVICIOS BIBLIOGRÁFICOS

Tesis que presenta: José Andrés Herrera Barragán

para obtener el grado de: Maestro en Ciencias

en la especialidad de: Ingeniería Eléctrica

Director de Tesis **Dr. Federico Sandoval Ibarra**

Guadalajara, Jalisco, Abril de 2009.

CLASIF.: TK165.G8 .H47 2009. ADQUIS.: 351-555 FEC. 4 2-510-04 PROCED DOD-04

10:160797 - 1001

# Diseño de un amplificador de potencia clase-E usando un transistor N-MOS de alto voltaje en una tecnología CMOS estándar

## Tesis de Maestría en Ciencias Ingeniería Eléctrica

Por:

José Andrés Herrera Barragán Ingeniero en Comunicaciones y Electrónica Universidad de Guadalajara 1998-2002

Becario de Conacyt, expediente no. 180876

Director de Tesis

Dr. Federico Sandoval Ibarra

CINVESTAV del IPN Unidad Guadalajara, Abril de 2009.

## Agradecimientos.

Pocas son las ocasiones en que públicamente se puede externar agradecimiento. Así, quiero expresar mi más profundo agradecimiento a Carmen Barragán y Andrés Herrera, mis padres, quienes son en gran medida responsables de este éxito personal. Además, quiero agradecer también a mis hermanos quienes, gracias a su apoyo y respeto, han colaborado en la consecución de este logro.

Mi agradecimiento, por supuesto, también se extiende al Doctor Juan Luís Del Valle; primero, al transmitirme y compartir parte de su conocimiento; después, por ser el guía de este trabajo; y finalmente, por confiar nuevamente en mi para que esta tesis pudiera ser concluida.

También quiero aprovechar estas líneas para agradecer al Doctor Federico Sandoval: gracias por su excelente enseñanza y por ser participe en la revisión y corrección de este trabajo.

En este mismo rubro, quiero agradecer al Doctor Raúl Loo, al Doctor Antonio Zenteno Ramírez y al Doctor Fernando Mendoza Hernández quienes contribuyeron en el escrutinio de esta Tesis.

No puedo olvidar mencionar al Doctor Juan Manuel Ramirez Arredondo. Sin su ayuda este trabajo no pudiera haber sido concluido.

Finalmente, y por supuesto no menos importante, quiero reconocer y agradecer la labor del CINVESTAV y CONACYT. Siempre estaré agradecido con este par de instituciones.

Sinceramente.

José Andrés Herrera Barragán.

## Diseño de un Amplificador de Potencia Clase-E usando un transistor N-MOS de alto voltaje en una tecnología CMOS Estándar.

#### Resumen.

#### Por José Andrés Herrera Barragan.

Las comunicaciones inalámbricas han adquirido vital importancia en nuestra vida diaria. Cada vez son más los dispositivos que funcionan sin necesidad de usar cables. Bajo estas circunstancias nuevos retos de diseño han aparecido. Uno de los más importantes es la eficiencia: como estos dispositivos pueden trabajar adecuadamente usando la menor cantidad posible de energía. Por otro lado, el reducir el tamaño de estos dispositivos también se ha convertido en un aspecto a resaltar en el diseño. En este contexto, los amplificadores de potencia que consumen poca energía y ocupan poco espacio son un tópico importante para los nuevos diseñadores.

Existen diferentes tipos de amplificadores de potencia. Cada uno de ellos pueden presentar características ideales de acuerdo a la aplicación para lo que son desarrollados. El amplificador de potencia clase E es considerado como uno de los ideales para aplicaciones que demandan bajo consumo de potencia. Muchos trabajos han sido presentados mostrando el diseño correcto de este tipo de amplificadores dependiendo del dispositivo que sea seleccionado como elemento activo del circuito. El conseguir una alta eficiencia es uno de los aspectos más estudiados para este tipo de amplificadores. Así, el presente trabajo se enfoca en este aspecto; particularmente, basado en el desarrollo de un transistor N-MOSFET capaz de soportar altos voltajes de rompimiento, tal como demanda esta aplicación.

El trabajo que se muestra a continuación, esta basado en principio, en el análisis físico del transistor N-MOSFET y posteriormente, en la simulación del circuito que pueda llevar al correcto análisis de los diferentes retos que están presente en la configuración seleccionada. Este trabajo pretende contribuir en el desarrollo de una metodología para el correcto diseño de un amplificador de potencia clase E, usando un transistor N-MOS como conmutador; además se presenta un solución integral y de bajo costo para este tipo de amplificadores. El diseño, análisis y desarrollo del transistor de alto voltaje que funciona como conmutador de este circuito, es también parte del presente trabajando; concluyendo con el posterior diseño físico y fabricación de dicho dispositivo.

Esta tesis se baso principalmente en dos trabajos: El primero de ellos presentador por D. K. Choi, en el cual expone una metodología para desarrollar el amplificador clase E basado en el análisis físico y el tamaño del transistor, teniendo como reto la estimación de los diferentes efectos indeseables que un transistor de mayor dimensión representa. El segundo trabajo, es el trabajo de tesis presentado por Isdriel Urías, en donde de una manera simple pero efectiva se describe una metodología para el desarrollo de un transistor de alto voltaje en una tecnología CMOS estándar.

El desarrollo de esta tesis fue realizado principalmente con la ayuda de las siguientes herramientas: MATLAB (para la simulación analítica del amplificador), T-Spice (para la simulación del circuito), L-Edit (para el diseño físico del transistor de alto voltaje), e ISE (para la estimación de los parámetros propios de la tecnología AMI 0.5 µm y la simulación del transistor a fabricar).

Cabe mencionar que los resultados analíticos y simulados fueron tal como se esperaban, sin embargo las mediciones físicas no correspondieron a lo esperado. En el análisis posterior se encontraron las posibles causas de esta discrepancia.

Algunos aspectos a resaltar de este trabajo, son el diseño de un dispositivo de alto voltaje en una tecnología de 0.5 µm dentro del grupo de diseño electrónico por primera vez. Además, es también digno de mencionar la estimación de los parámetros tecnológicos que se realizó de dicha tecnología. Como aspectos a mejorar quedan la nueva fabricación del dispositivo de alto voltaje con los parámetros adecuados para su correcto funcionamiento. Además, de que algunos aspectos en el análisis del amplificador fueron tomados como ideales (por ejemplo, la red de carga del circuito del amplificador).

# A Class-E Power Amplifier design using a High Voltage N-MOS transistor in a CMOS standard technology.

#### Summary. By Jose Andres Herrera Barragan.

Wireless communications have acquired critical importance in the day by day life. More devices are incorporated to this new technology daily. It is common to see how not just cell phones and notebooks but also a huge number of other wireless devices increased considerably. From this perspective, new design challenges show up. One of the most important is efficiency: how a device can work and transmit using the lowest possible energy. In other hand, miniaturization also has appeared as a really relevant aspect when designing. In this context, power amplifiers that consume low energy and have small real state have become a worth topic for new designers. Hence, the problem consists in designing a power amplifier that meets both above at low cost.

There are different kind of power amplifiers. Features that present each of them might be consider as ideal, depending of the application it is developed to. Class E PA is considered as one of the ideal for applications that demand low power at high frequencies, when linearity is not really important. Many works have been presented showing the correct designing according to the selected active device, developing all class of analysis that help to estimate the different effects to be maximized or minimized, depending of the application. To get high efficiency has been one of the most important topics in different studies. Therefore, this work focuses on this aspect, but in this case, based on the develop of a NMOS transistor able to support high breakdown voltages in a standard CMOS technology.

The design shown here is based on first, a physical analysis of the device, and then a simulation analysis capable to address all the different issues presented in this kind of topology. This work contributes to develop a methodology for the design of a class E power amplifier when MOS transistor is used, and also presents a cheap and integral solution for these kind of amplifiers. The design and analysis of the high voltage transistor that works as active devices has been also part of this work, finishing with the physical design and corresponding fabrication.

This thesis was based mainly in other two works: First, the physical analysis for a Class-E PA presented by D. K. Choi. This analysis provides a methodology to develop a class E PA based on the size of the NMOS transistor, dealing with all the undesirable effects that a big device represents. The second work is the thesis presented by Isdriel Urias, where a simple but effective methodology to get a high breakdown voltage device in CMOS standard technology was detailed.

For the study and analysis in this thesis different tools were used, mainly:

Matlab: To get an analytical prediction of the amplifier behavior.

T-Spice: To run needed simulations of the suggested circuit. L-Edit: To develop the layout for device fabrication.

ISE: To estimate technology parameters and also to predict the behavior of the device.

Simulation results were as expected, but physical results were not as the design demanded. However, the further analysis allowed in some way to found the root cause of the problem.

Something that was new in this thesis within "electronic design" group, was the design and fabrication of a high voltage device in the 0.5 um technology. The proposal of using a structural methodology based on transistor size was also one of the highlights of this thesis; of course this methodology was proposed by [Choi], however this work complements his analysis going deeper in some other aspects and obviously proposing the high voltage device as solution to get a better performance. Besides this, the obtaining of most of AMI 0.5um technology parameters through ISE is worthy of mentioning.

On the lowlights, the failure on the high voltage device fabrication can be mentioned; however this aspect allow us to know more about this technology, specifically the diffusion of N-Well mask. Besides this, some other aspects could be cited: the load circuit in PA-E was taken as ideal, and no analysis of this topic was discussed.

As future research, the re-fabrication of the high voltage device —this time with the "correct" length parameters- is proposed, in order to proceed with the connection of the complete amplifier system to characterize it and correlate it with corresponding simulations.

## **CONTENIDO**

| AGRADECIMIENTOS                                                                                    |          |

|----------------------------------------------------------------------------------------------------|----------|

| RESUMEN                                                                                            |          |

| CONTENIDO                                                                                          | VII      |

| ÍNDICE DE FIGURAS                                                                                  | X        |

| ÍNDICE DE TABLAS                                                                                   | XIII     |

| CAPÍTULO 1                                                                                         |          |

| INTRODUCCIÓN                                                                                       |          |

| 1.1 Motivación.                                                                                    | 2        |

| 1.2 Objetivo                                                                                       | 4        |

| 1.3 La tecnología CMOS                                                                             | 5        |

| 1.4 Transistores NMOS de drenador extendido                                                        | 6        |

| 1.5 Organización de la tesis                                                                       | 6        |

| Referencias                                                                                        | 8        |

| CAPÍTULO 2                                                                                         |          |

| AMPLIFICADORES DE POTENCIA EN RF                                                                   | 9        |

| 2.1 Conceptos básicos2.1.1 Diferencia entre un amplificador de potencia y un amplificador de señal | pequeña  |

| 2.1.2 Eficiencia (Eff)                                                                             | 10       |

| 2.1.3 Ganancia (G)                                                                                 |          |

| 2.1.4 Eficiencia de Potencia añadida (PAE, <i>Power Added Efficiency</i> ) 2.1.5 Linealidad        | 11<br>11 |

| 2.2 Tipos de amplificadores                                                                        |          |

| Z Z AMDITICADORS DE DOTENCIA EN MODO FUENTE DE Corriente                                           | 12       |

| Amplificador de potencia clase A                           |     |

|------------------------------------------------------------|-----|

| Amplificador de potencia clase B                           | 14  |

| Amplificador de potencia clase AB                          | 16  |

| Amplificador de potencia clase C                           | 16  |

| 2.2.2 Amplificadores de potencia en Modo Conmutado         | 17  |

| Conmutación Suave y Conmutación rígida                     | 18  |

| Amplificador de potencia clase D                           | 19  |

| Amplificador de potencia clase F                           | 20  |

| 2.2 Conclusiones                                           | 21  |

| Referencias                                                | 22  |

| CAPÍTULO 3                                                 |     |

| EL AMPLIFICADOR DE POTENCIA CLASE E                        | 23  |

| 3.1 El funcionamiento del amplificador de potencia clase E | 24  |

| 3.2 Diseño de un amplificador de potencia clase E Ideal    | 29  |

| 3.3 La resistencia de encendido (R <sub>ON</sub> )         | 34  |

| 3.4 Diseño en base al dimensionamiento del transistor      | 37  |

| 3.4.1 Dimensionamiento del transistor                      |     |

| 3.4.2 Simulación en SPICE                                  | 49  |

| 3.5 Pérdidas de potencia en los componentes pasivos        | 51  |

| 3.6 Entonación del circuito y resultados del diseño final  | 51  |

| 3.7 Conclusiones de la simulación de SPICE                 | 55  |

| 3.7 Comentarios finales                                    | 56  |

| Referencias                                                | 58  |

| CAPÍTULO 4                                                 |     |

| TRANSISTOR DE ALTO VOLTAJE                                 | 61  |

| 4.1 Límites de la tecnología CMOS estándar                 | 62  |

| 4.1.1 El efecto de los electrones calientes en el canal    |     |

| 4.1.2. Rompimiento por Avalancha                           |     |

| 4.1.3. Rompimiento en la superficie.                       |     |

| A 1 A Kompiniento en el óvido de la compuerta              | GA. |

| 4.2 Extracción de los parámetros de la tecnología AMI 0.5 μm           | - 64 |

|------------------------------------------------------------------------|------|

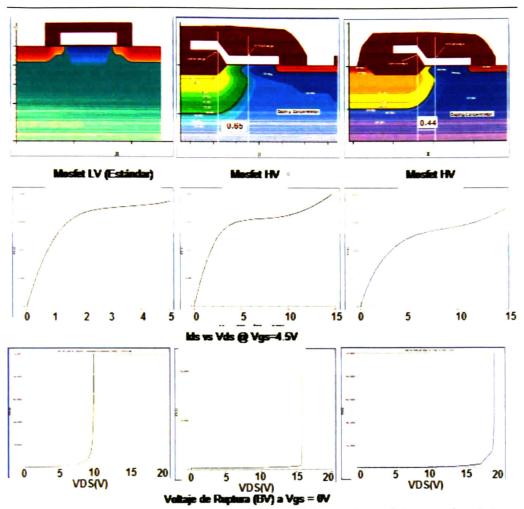

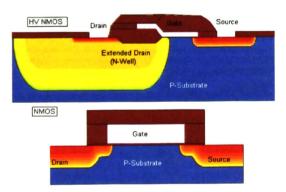

| 4.3. El transistor XD MOS                                              | - 69 |

| 4.3.1. Tecnología de fabricación de un transistor NMOS de alto voltaje | - 72 |

| stor NMOS de alto voltaje                                              | - 73 |

| 4.5. Implementación del diseño y consideraciones de Layout             | - 78 |

| 4.6. Mediciones y resultados                                           | - 82 |

| 4.7. Conclusiones                                                      | - 86 |

| Referencias                                                            | - 87 |

| CAPÍTULO 5                                                             |      |

| CONCLUSIONES GENERALES                                                 | - 89 |

| APENDICE                                                               |      |

| PUBLICACIONES                                                          | - 92 |

# Índice de Figuras.

## Capítulo 1

| Fig. 1.1 Diagrama a bloques de un sistema transmisor-receptor diseñado con diferentes tecnologías                                                                                                 | 2        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Fig. 1.2 Diagrama básico de un sistema transmisor-receptor                                                                                                                                        | 3        |

| Fig. 1.3 Espectro radioeléctrico                                                                                                                                                                  | 4        |

| Capítulo 2                                                                                                                                                                                        |          |

| Fig. 2.1 Configuración de un amplificador en fuente común                                                                                                                                         | 10       |

| Fig. 2.2. Configuración básica de los amplificadores de potencia en modo fuente de corriente                                                                                                      | 12       |

| Fig. 2.3 Línea de carga y forma de onda de la corriente de salida para un amplificador clase A                                                                                                    | 13       |

| Fig. 2.4 Línea de carga y forma de onda de la corriente de salida para un amplificador clase B                                                                                                    | 15       |

| Fig. 2.5 Línea de carga y forma de onda de la corriente de salida para un amplificador clase C                                                                                                    | 17       |

| Fig. 2.6 Diagrama simplificado de un amplificador conmutado para simplificar la diferencia entre conmutación suave y conmutación rígida                                                           | 18       |

| Fig. 2.7 Circuito simplificado del amplificador clase D y sus formas de onda asociadas                                                                                                            | 20       |

| Fig. 2.8 Circuito simplificado del amplificador clase F y sus formas de onda asociadas                                                                                                            | 21       |

| Capítulo 3                                                                                                                                                                                        |          |

| Fig. 3.1 Modelo eléctrico de un amplificador clase E ideal                                                                                                                                        | 24       |

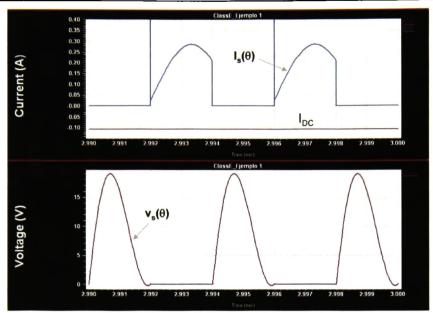

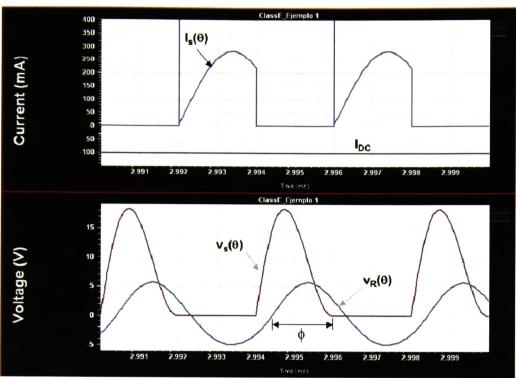

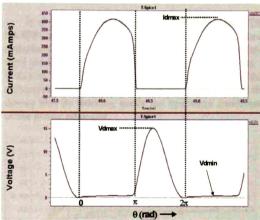

| Fig. 3.2 Formas de onda de corriente y voltaje normalizadas en el conmutador de un amplificador clase E                                                                                           | 25       |

| Fig. 3.3 Efectos del valor de $L_{chk}$ en la variación de la corriente en el inductor de choque. (a) $L_{chk}$ =5 mH, (b) $L_{chk}$ = 10Mh                                                       | 30       |

| Fig. 3.4 Efectos del valor de $L_{chk}$ en el tiempo en el cual se alcanza un estado estable del voltaje de salida en el amplificador. (a) $L_{chk} = 5 \text{mH}$ , (b) $L_{chk} = 10 \text{mH}$ | 31       |

| Fig. 3.5 Formas de Onda en el conmutador                                                                                                                                                          | 32       |

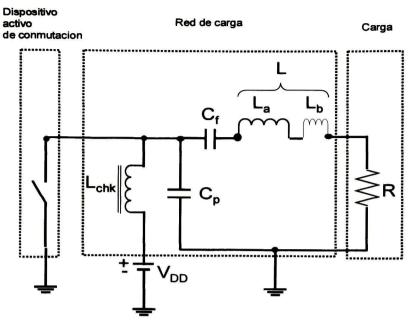

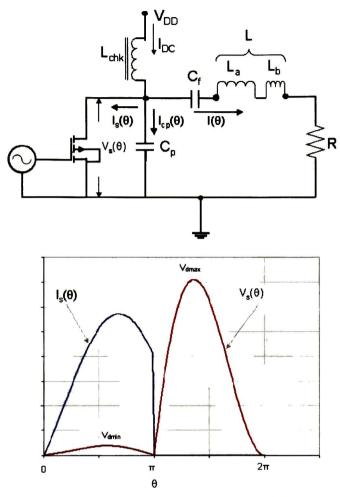

| Fig. 3.6 Detalle del voltaje en el conmutador al momento de cierre del mismo<br>Fig. 3.7 Modelo eléctrico corregido del amplificador clase E                                                      | 32<br>33 |

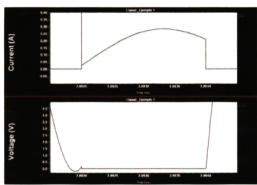

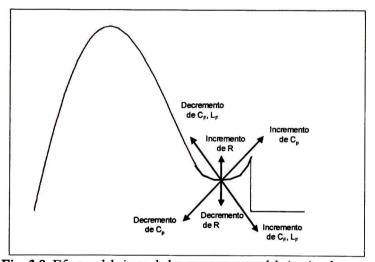

| Fig. 3.8. Efectos del ajuste de las componentes del circuito de carga<br>Fig. 3.9 Forma de ondas en el conmutador después del ajuste                                                              | 33<br>34 |

| Fig. 3.10 Circuito eléctrico del AP clase E con un transistor NMOS y sus formas de onda asociadas                                                                                                 | 35       |

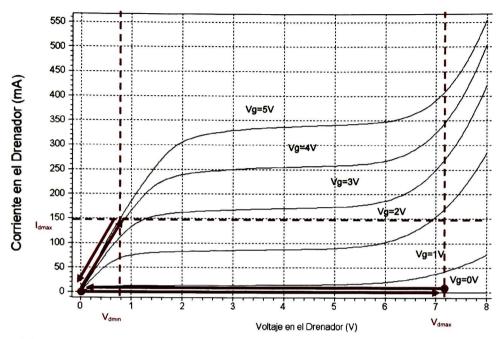

| Fig. 3.11 Rectas de Carga del amplificador clase E en un transistor NMOS de la                                                                                                                    |          |

| tecnología AMI 0.5µm                                                                                                                                                                              | 36       |

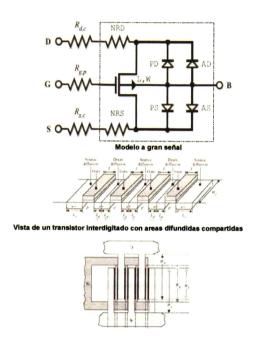

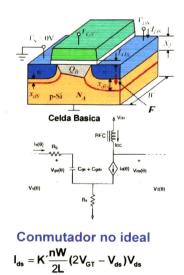

| Fig. 3.12 Concepción de Transistores inter-digitados<br>Fig. 3.13 Celda Básica y factor de multiplicación                                                                                         | 38<br>38 |

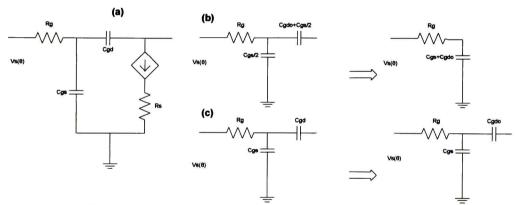

| Fig. 3.14 Circuito equivalente de entrada para un N-MOSFET                                        | 39  |

|---------------------------------------------------------------------------------------------------|-----|

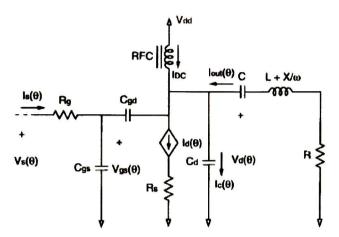

| Fig. 3.15 Circuito completo del AP clase E sustituyendo el FET con su modelo                      |     |

| equivalente                                                                                       | 42  |

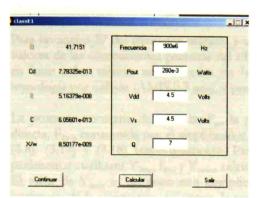

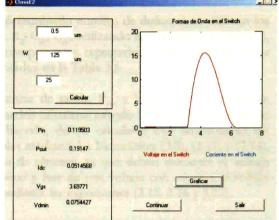

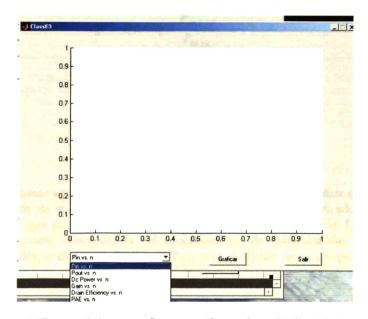

| Fig. 3.16 Ambiente visual del programa desarrollado en MatLab para el análisis del                |     |

| AP                                                                                                | 44  |

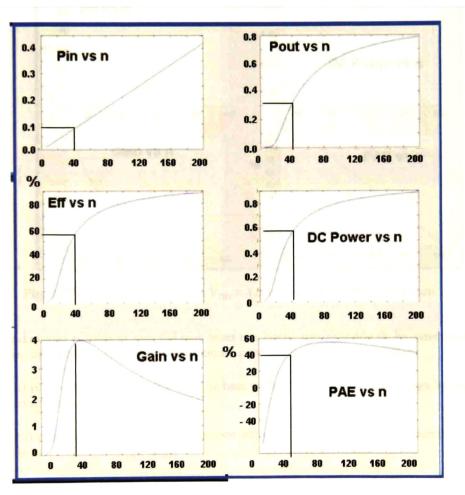

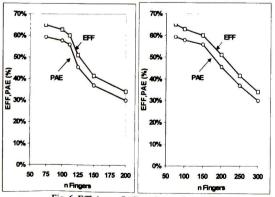

| Fig. 3.17a Figuras de merito para $V_{DD} = 2 \text{ V}$ , Pout=1W, W=125 $\mu m$                 | 47  |

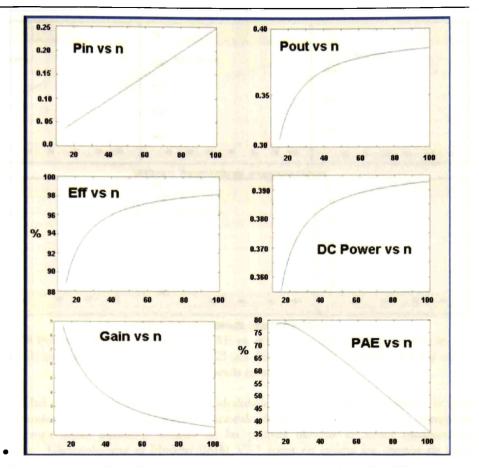

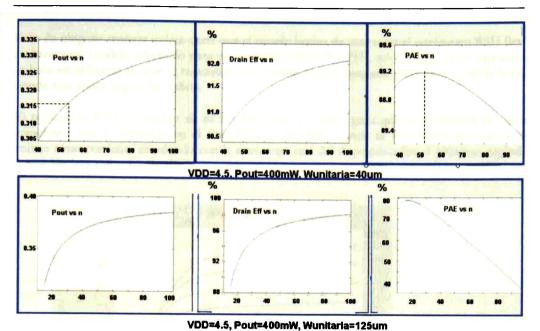

| Fig. 3.17b Figuras de merito para $V_{DD} = 4.5 \text{ V}$ , Pout =0.400 W, W=125 $\mu$ m         | 48  |

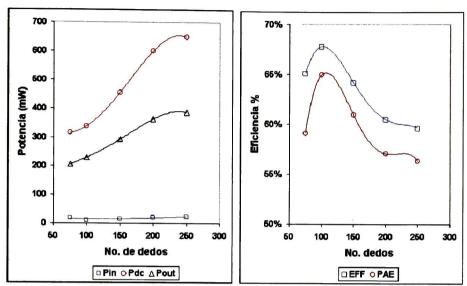

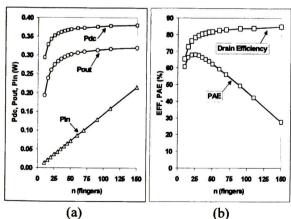

| Fig. 3.18 Potencia de salida, Eficiencia y PAE vs. el factor de multiplicación n para un          |     |

| transistor de ancho W igual a 40 µm y 125 µm. Para un voltaje V <sub>dd</sub> igual a 4.5 V y una |     |

| potencia de salida deseada igual a 400 mW                                                         | 49  |

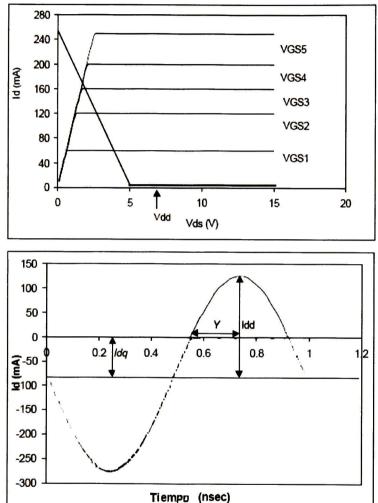

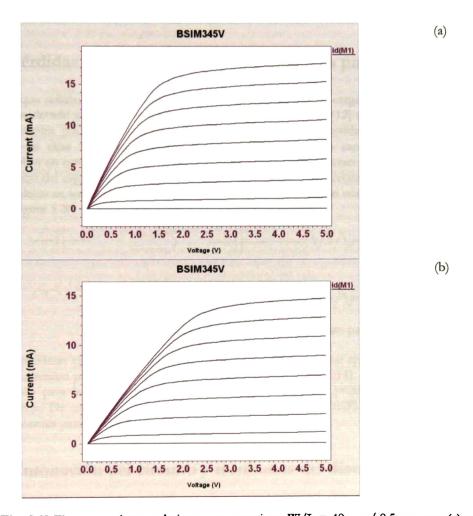

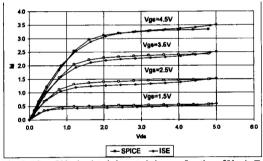

| Fig. 3.19 Figuras corriente-voltaje para un transistor $W/L = 40 \mu m / 0.5 \mu m$ para (a)      | -   |

| un modelo BSIM3 de un transistor convencional y (b) el mismo modelo con                           |     |

| RSH=1000 Ohm/cuadro para propósitos de simulación del transistor de alto voltaje.                 |     |

| La curva con el voltaje máximo en la compuerta es igual 4.5 V                                     | 50  |

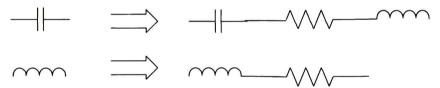

| Fig. 3.20. Modelo equivalente de componente pasivos                                               | 51  |

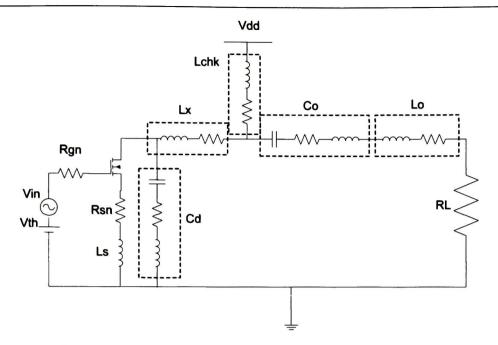

| Fig. 3.21 Circuito final simulado en T-Spice para el diseño propuesto del AP clase E              | 52  |

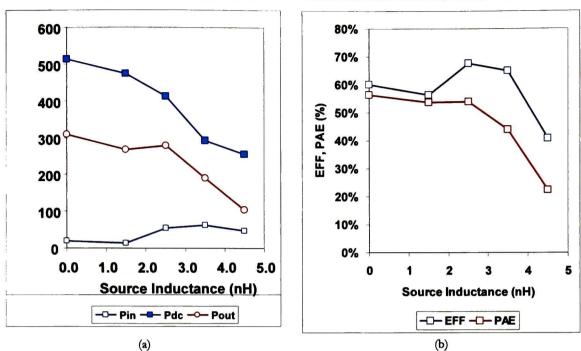

| Fig. 3.22 Efecto de la inductancia parásita en la fuente del transistor para las                  | 32  |

| características del AP. (a)Potencia de entrada, salida y DC; (b) Eficiencia y Eficiencia          |     |

| Añadida                                                                                           | 53  |

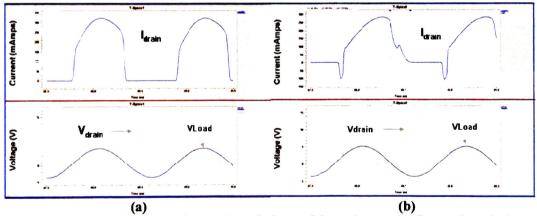

| Fig. 3.23 Efecto de la inductancia parásita en la fuente del transistor en las formas de          | 33  |

| onda de corriente y voltaje del amplificador simulado. (a) $L_c = 0$ ; (b) $L_c = 2.5 \mu H$      | 53  |

| Fig. 3.24 Factores de mérito simulados en SPICE usando BSIM3 vs. el factor de                     | 33  |

| multiplicación, para un $V_{DD} = 4.5 \text{ V}$                                                  | 54  |

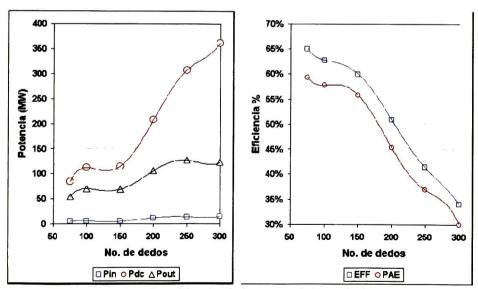

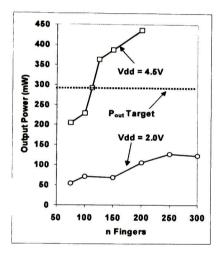

| Fig. 3.25 Factores de mérito simulados en SPICE usando BSIM3 vs. el factor de                     | 34  |

| multiplicación, para un VDD = 2.0 V                                                               | 54  |

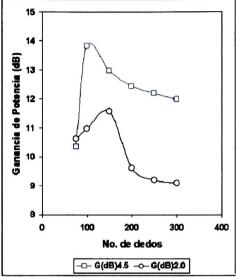

| Fig. 3.26. Valores simulados de Potencia de Salida y Ganancia de potencia (dB) vs. el             | 34  |

| factor de multiplicación para $V_{DD} = 4.5 \text{ V y } V_{DD} = 2 \text{V}$                     | 55  |

| ractor de munipileación para v <sub>DD</sub> = 4.3 v y v <sub>DD</sub> = 2 v                      | 33  |

| Capitula 4                                                                                        |     |

| Capítulo 4                                                                                        |     |

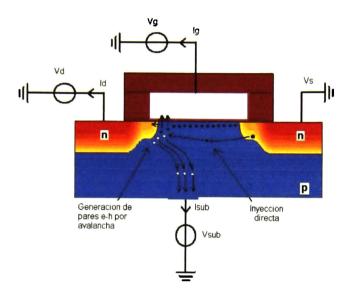

| Fig. 4.1 Ilustración del fenómeno de electrones calientes en el canal                             | 62  |

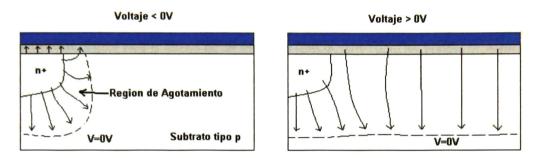

| Fig. 4.2 Ilustración del efecto de aplicar un voltaje en el field plate que se encuentra          |     |

| encima de una unión p-n                                                                           | 64  |

| Fig. 4.3 Dispositivo N-MOSFET diseñando en MDRAW de ISE para buscar la                            |     |

| correlaciona con el modelo simulado en T-Spice                                                    | 66  |

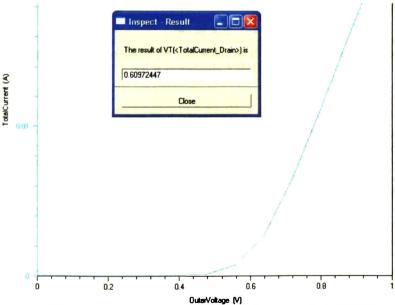

| Fig. 4.4 Obtención del voltaje de umbral a través de DESIS                                        | 66  |

| Fig. 4.5 Comparación de las curva I-V obtenidas en ISE y T-Spice para un transistor               |     |

| NMOS                                                                                              | 67  |

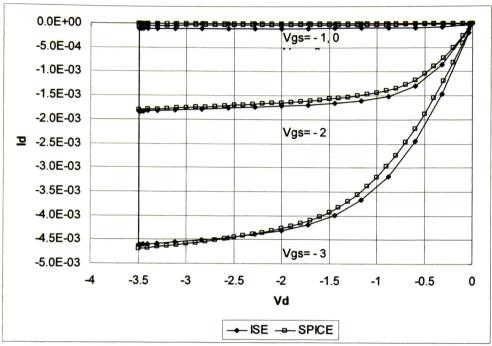

| Fig. 4.6 Comparación de las curva I-V obtenidas en ISE y T-Spice para un transistor               |     |

| PMOS                                                                                              | 68  |

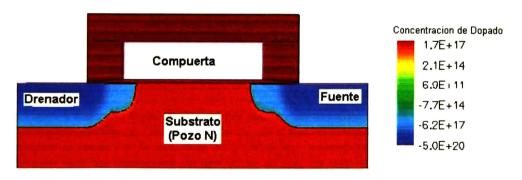

| Fig. 4.7 Concentración de dopado para el transistor PMOS simulado en ISE                          | 68  |

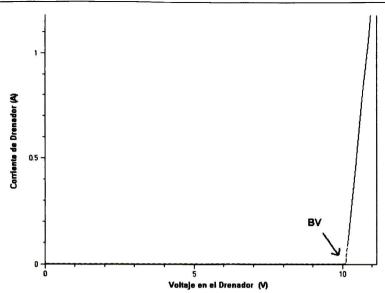

| Fig. 4.8 Obtención del voltaje de ruptura (BV) a través de la simulación directa en               |     |

| ISE                                                                                               | 69  |

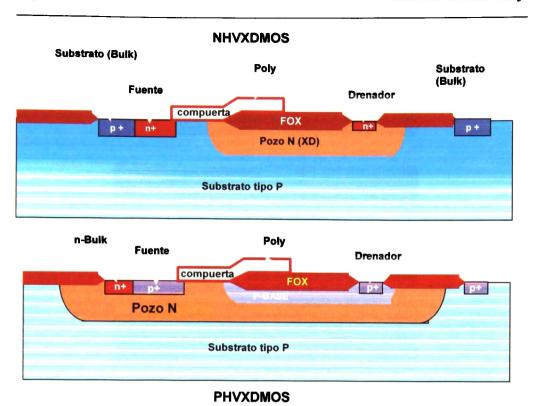

| Fig. 4.9 Sección transversal de un transistor para alto voltaje, de drenador extendido            | -   |

| tipo P y tipo N                                                                                   | 70  |

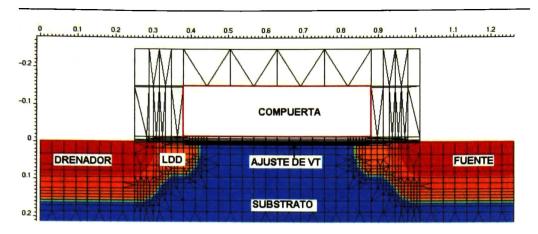

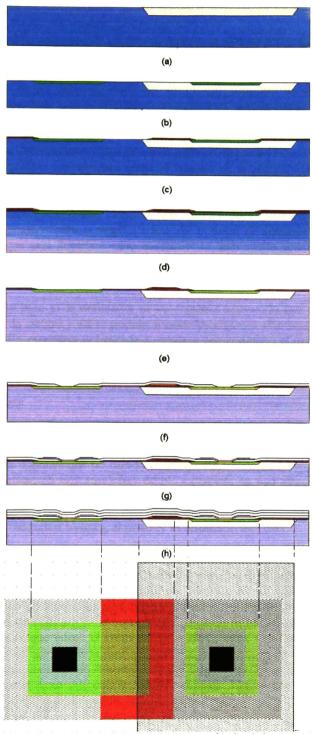

| * * *                                                                                             | . 0 |

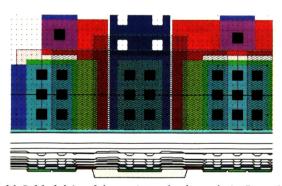

| Fig. 4.10 Creación del transistor HVXDNMOS visto desde el diseño del layout en        |    |

|---------------------------------------------------------------------------------------|----|

| L-Edit                                                                                | 71 |

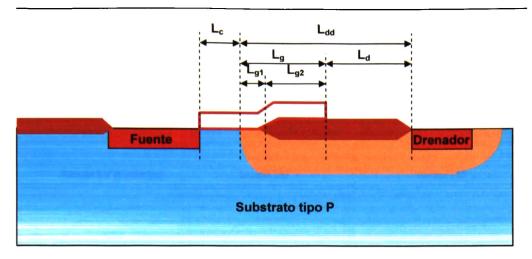

| Fig. 4.11 Parámetros de diseño del HVXDNMOS                                           | 73 |

| Fig. 4.12 Voltaje de ruptura y resistencia de encendido (pendiente de la curva de     |    |

| voltaje-corriente), para un transistor N-MOS convencional y un HVNMOS con dos         |    |

| valores distintos para L <sub>21</sub>                                                | 75 |

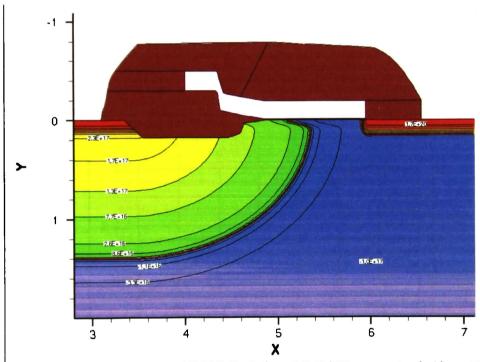

| Fig. 4.13 Dispositivo HVXDNMOS diseñado en MDRAW para su simulación en                |    |

| ISE                                                                                   | 76 |

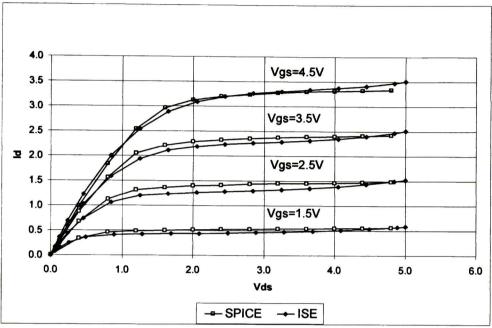

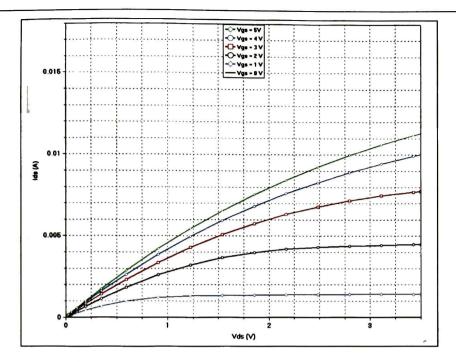

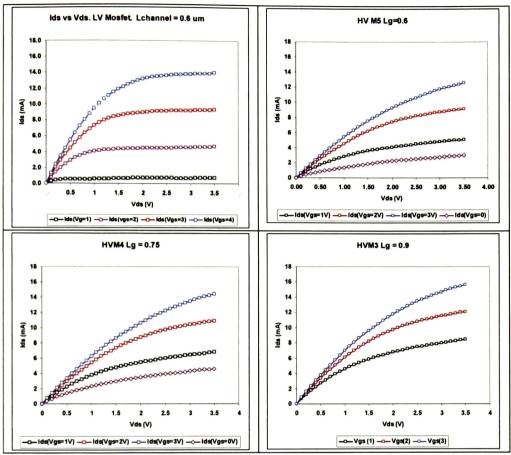

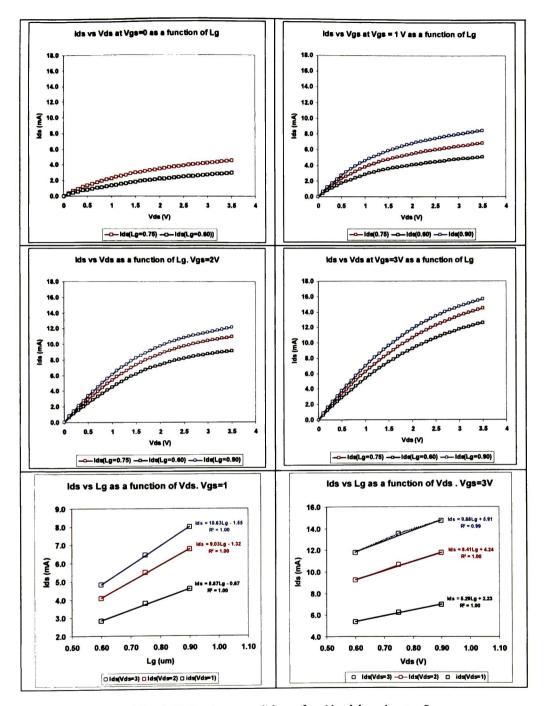

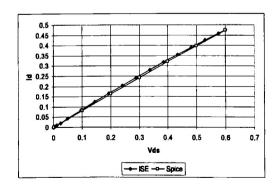

| Fig. 4.14 Curvas de I-V para el transistor XD HV-NMOS. Lg = 0.75 μm                   | 77 |

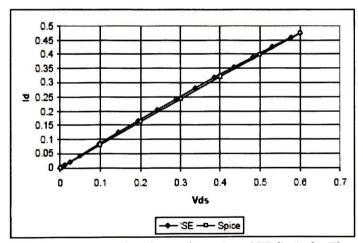

| Fig. 4.15 Comparación de la región lineal para el transistor HV diseñado. El modelo   |    |

| de Spice corresponde al modelo BSIM3 con la modificación propuesta en el capitulo     |    |

| anterior para el parámetro R <sub>SH</sub>                                            | 77 |

| Fig. 4.16 Comparación entre un transistor convencional y uno de alto voltaje desde el |    |

| punto de vista de layout                                                              | 78 |

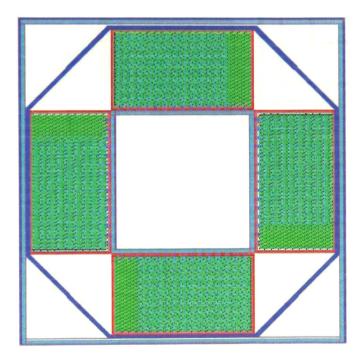

| Fig. 4.17 Estructura de layout propuesta para el transistor de W=800 μm               | 79 |

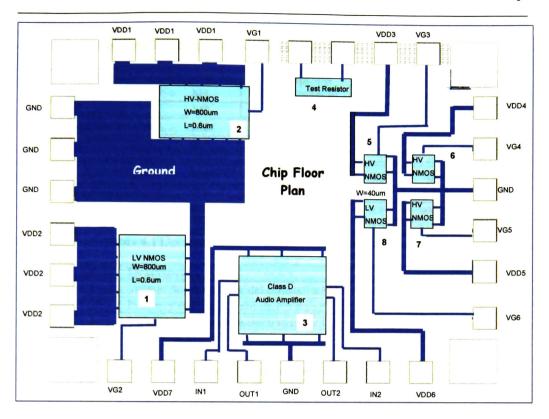

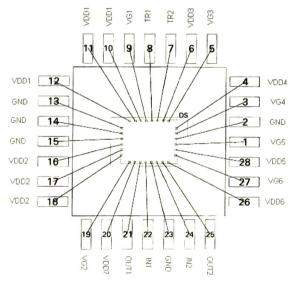

| Fig. 4.18 Disposición final del chip mandado a fabricar                               | 80 |

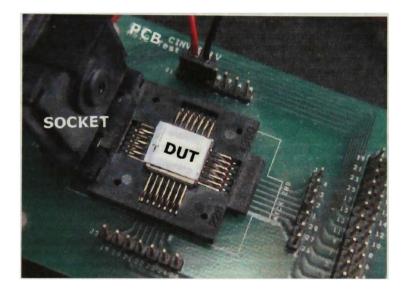

| Fig. 4.19 Tarjeta usada para realizar las mediciones en el chip                       | 82 |

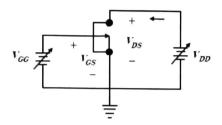

| Fig. 4.20 Configuración usada para realizar las mediciones I-V                        | 83 |

| Fig. 4.21 Características I-V medidas en los cuatro dispositivos de W=40 μm           |    |

| fabricados                                                                            | 84 |

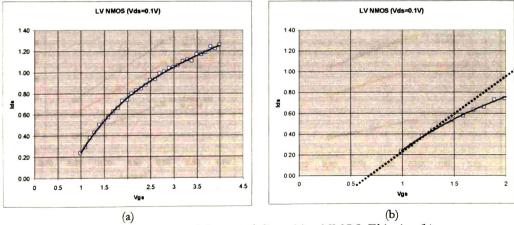

| Fig. 4.22 Voltaje de umbral medido para el dispositivo NMOS. El inciso (b) muestra    |    |

| un acercamiento para poder estimar el valor                                           | 84 |

| Fig. 4.23 Corriente medida en función del parámetro Lg                                | 85 |

|                                                                                       |    |

## Índice de tablas.

## Capítulo 1

| Tabla 1.1 Algunos estándares de comunicación                                        | 5  |

|-------------------------------------------------------------------------------------|----|

| Capítulo 3                                                                          |    |

| Tabla 3.1 Resumen de ecuaciones que describen el comportamiento de un               |    |

| amplificador clase, usando condiciones ideales y un ciclo de trabajo del 50%        | 2  |

| Tabla 3.2 Resumen de ecuaciones que describen el valor de las componentes           |    |

| discretas de un AP clase E. Condiciones ideales y un ciclo de trabajo del 50 %      | 28 |

| Tabla 3.3 Resumen de ecuaciones que describen el valor de las componentes           |    |

| discretas de un AP clase E incluyendo el valor del ángulo de fase φ. Condiciones    |    |

| ideales y un ciclo de trabajo del 50 %                                              | 28 |

| Tabla 3.4 Variables independientes propuestas para el diseño de AP clase E          | 29 |

| Tabla 3.5 Valores de las componentes discretas para los dos casos ideales de diseño | 30 |

| Tabla 3.6 Valores tecnológicos obtenidos de la ultima corrida de MOSIS              | 41 |

| Tabla 3.7 Características finales del AP diseñado                                   | 50 |

| Capítulo 4                                                                          |    |

| Tabla 4.1 Descripción de los dispositivos fabricados en el chip                     | 81 |

| Tabla 4.2 Descripción de los pines del chip                                         | 81 |

## Capítulo 1

#### Introducción.

L presente trabajo se centra en el análisis y diseño de un amplificador de potencia clase E, capaz de operar en el estándar GSM utilizando una tecnología CMOS convencional. Como es sabido, los amplificadores de potencia son responsables de gran parte del consumo de energía en los sistemas móviles, y habrá que tener en cuenta que en dichos sistemas, el uso de baterías es un punto crucial, puesto que el periodo de funcionamiento estará limitado al tiempo en que estos sistemas puedan ser usados sin necesidad de ser recargados.

Así, en este trabajo se exponen los conceptos básicos de los amplificadores de potencia, los distintos tipos que existen, y las ventajas y desventajas de los mismos, para finalmente considerar el amplificador de potencia clase E como el idóneo para la aplicación que se propone; así mismo, se presentará un análisis completo para el diseño óptimo del amplificador clase E, basado en las características propias de un transistor CMOS. Esto llevará a cuestionar las limitaciones de la topología utilizada y a la consecuente propuesta del uso de un dispositivo de alto voltaje para obtener mayores prestaciones en dicho amplificador.

Finalmente, se analizará la opción de crear el transistor de alto voltaje usando la tecnología CMOS convencional; se efectuará el diseño de dicho transistor con la finalidad de obtener los resultados que permitan la fabricación del dispositivo, para después obtener los datos experimentales que sustenten el diseño y la solución para el amplificador de potencia propuesto.

Capítulo 1 Introducción.

#### 1.1 Motivación.

El rápido crecimiento de las comunicaciones inalámbricas en el mundo actual ha tenido como consecuencia un aumento en el diseño de circuitos integrados para radiofrecuencia (RFIC). Cada vez son más los productos que ofrecen la posibilidad de comunicación sin la necesidad de cables, y el número de usuarios de dichos productos va en aumento exponencial [1]. Ejemplos claros de lo mencionado anteriormente son el uso cada vez más amplio de teléfonos celulares así como de teléfonos y módems inalámbricos.

Dentro de este panorama de constante cambio es necesario contar con sistemas que cada vez ofrezcan una mayor versatilidad en su funcionamiento sin perder de vista el costo. Además otro aspecto muy importante es la miniaturización de dichos sistemas lo que demanda un esfuerzo de los diseñadores para conseguir mayores niveles de integración.

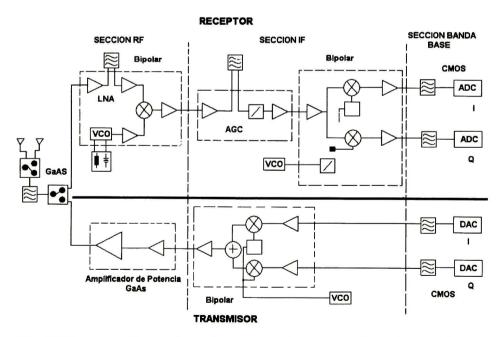

Es por esto que el diseño de sistemas de transmisión y recepción que disipen poca potencia ha llegado a ser un reto para quien actualmente diseña sistemas de comunicación inalámbricos; y debido a las tendencias actuales, lo seguirá siendo durante futuras generaciones. Los diseñadores cuentan con un gran número de posibilidades en cuanto a tecnologías se refiere (CMOS, BICMOS, Bipolar, GaAS MESFET, HBT, etc.). Generalmente para el desarrollo de un sistema completo, se utiliza una combinación entre las diferentes tecnologías de acuerdo con las características propias de cada bloque, como se observa en la Figura 1.1 [2].

Fig. 1.1 Diagrama a bloques de un sistema transmisor-receptor diseñado con diferentes tecnologías.

Capítulo 1 Introducción.

Capitalo I

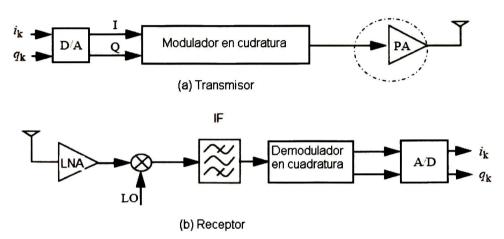

La estructura básica de un sistema de transmisión y recepción de información para RF se muestra en la Figura 1.2 y su funcionamiento en términos generales es como sigue:

En el transmisor (Fig. 1.2a), los datos digitales son codificados inicialmente, luego los canales independiente para datos (I y Q) son mezclados por un modulador en cuadratura, en seguida la señal resultante es llevada a la frecuencia RF de la portadora. Después de ser filtrada, la señal entra al amplificador de potencia cuya salida esta conectada a la antena y esta, a su vez, radiará la información haciendo que la transmisión esté completa.

En el receptor sucede lo contrario (Fig. 1.2b), la señal recibida por la antena es filtrada para seleccionar la RF de interés para después entrar en el "amplificador de bajo ruido" (LNA). La señal resultante es filtrada y llevada a una frecuencia intermedia (IF), luego la señal es separada en sus componentes I y Q, para finalmente ser digitalizada y poder ser procesada [3].

Fig. 1.2 Diagrama básico de un sistema transmisor-receptor.

Dentro de estos sistemas, los amplificadores de potencia, son responsables de un significativo consumo de la potencia total del sistema; por lo tanto, para este tipo de aplicaciones se requieren amplificadores que sean capaces de tener eficiencias altas de conversión de energía (de DC a RF), y que disipen así poca potencia.

Así pues, existe la motivación de diseñar un amplificador que sea capaz de tener una eficiencia alta, pero que por otro lado sea de bajo costo y que además, pueda ser integrado fácilmente en un sistema completo.

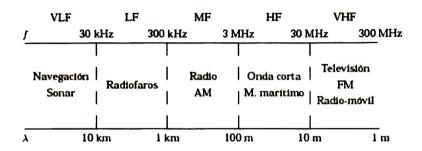

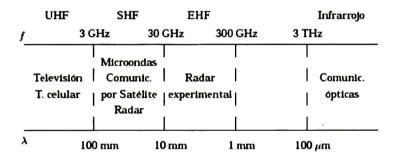

Existen diferentes tipos de amplificadores de potencia que ofrecen distintas ventajas de acuerdo a la aplicación, pero son los amplificadores en modo de conmutación los que ofrecen en teoría (y generalmente en la práctica) una mayor eficiencia. Recientemente el AP clase F y en especial el clase E han tenido un mayor estudio y han sido motivo de investigación y desarrollo para las aplicaciones RF [4]. Así, el amplificador clase E es una buena opción para el desarrollo de aplicaciones de comunicación móvil, las cuales se encuentran dentro de la banda de frecuencias ultra altas (UHF). En el Capítulo 3 se analizará con mayor detalle las ventajas de

este amplificador (clase E) sobre otros amplificadores para la aplicación propuesta en este trabajo. En la Figura 1.3 podemos ver el rango completo de frecuencias para el área considerada RF, así como las distintas aplicaciones que se tienen para cada una de las bandas.

Fig. 1.3 Espectro radioeléctrico.

#### 1.2 Objetivo.

Como se ha señalado una de las aplicaciones de RF es la de las comunicaciones móviles. En la Tabla 1.1 tenemos las características de algunos estándares para las comunicaciones inalámbricas, incluyendo la frecuencia. De esta manera, este trabajo tiene como objetivo el diseño de un amplificador de potencia que sea capaz de operar en una de las tecnologías actuales y de gran demanda, como lo es el estándar GSM [5]. Sus características serán una frecuencia de 900 MHz y una capacidad para la potencia de salida de 280 mW (25 dBm), ya que estas son las especificaciones de dicho estándar

Cabe mencionar que debido a los requerimientos de eficiencia y frecuencia ya señalados y en base al análisis que se hará en el Capítulo 2, se ha escogido el AP clase E como el idóneo para este diseño. Además, por lo que se mencionará en la Sección 1.3 y 1.4, se propone la tecnología CMOS usando un dispositivo de alto voltaje (XDNMOS) que sea capaz de cubrir las

necesidades de voltaje de ruptura (BV, por sus siglas en inglés) y resistencia de encendido (R<sub>ON</sub>), para tener un AP con mayores prestaciones.

| Parámetro               | NADC      | IS-95 CDMA | GSM      | DECT      |

|-------------------------|-----------|------------|----------|-----------|

| RF Tx.                  | 824-849   | 1860-1910  | 890-915  | 1880-1900 |

| Frec. (MHz)             |           |            |          |           |

| Acceso Múltiple         | TDMA/FDM  | CDMA/FDM   | TDMA/FDM | TDMA/FDM  |

| Numero de Canales       | 832       | 20         | 124      | 10        |

| Espacio para cada canal | 30kHz     | 1.25MHz    | 200kHz   | 1.728MHz  |

| Modulación              | π/4-DQPSK | π/4-DQPSK  | GMSK     | GFSK      |

Tabla 1.1 Algunos estándares de comunicación.

Es necesario señalar que toda la labor de diseño será desarrollada en la tecnología CMOS AMI 0.5 µm debido a que es una de las tecnologías a la que se tiene acceso a través del servicio de implementación de la tecnología CMOS (MOSIS) y que es capaz de alcanzar la frecuencia requerida.

#### 1.3 La tecnología CMOS.

Hay que destacar que las capacidades de la tecnología CMOS hacen que esta sea particularmente atractiva para los diseñadores, pues como es bien conocido, su bajo costo, su gran capacidad de integración, su bajo consumo de potencia, así como la gran cantidad de literatura y software que se puede encontrar para su desarrollo [6], hacen de esta tecnología una de las más utilizadas en el mundo de los dispositivos electrónicos.

Sin embargo, en la búsqueda del desarrollo de AP existen para esta tecnología una serie de limitantes o desventajas para las cuales se han propuesto distintas alternativas o soluciones en la literatura. Los retos que se pueden encontrar para el diseño de amplificadores de potencia en esta tecnología son:

- 1. El relativamente bajo voltaje de ruptura entre las terminales de drenadorfuente y compuerta-fuente en los transistores CMOS, hacen que esta

tecnología tenga una desventaja para el desarrollo de AP puesto que en

algunas clases tales como el clase B y F, el voltaje en el drenador se duplica

con respecto al voltaje de alimentación e incluso se triplica en el caso del AP

clase E [7]. Así, el voltaje de alimentación (V<sub>DD</sub>) tendrá que ser muy bajo,

limitando la potencia de salida que se puede alcanzar además de la eficiencia.

- 2. En la mayoría de las tecnologías CMOS que existen, el substrato se encuentra relativamente muy dopado, lo que provoca una interacción con los dispositivos creándose corrientes de fuga que pueden llegar a afectar la estabilidad del amplificador.

- 3. Otro reto con el que un diseñador se encuentra, es que los modelos que existen para los transistores CMOS en general no han sido lo suficientemente desarrollados para RF, así que probablemente no se pueden tener datos muy exactos para este tipo de aplicaciones.

Capítulo 1 Introducción.

Como las corrientes que se maneja en un AP son relativamente altas puede llegar a existir electro migración causando de esta manera, la degradación del dispositivo.

Dentro de estas desventajas, la primera de ellas es la que tiene un especial interés en este trabajo. Una de las estrategias que se han propuesto para solucionarla, es el uso de múltiples etapas que eviten tener voltajes drenador-fuente altos, sin embargo una mejor solución seria el diseño de transistores capaces de tener mayores voltajes de ruptura (*Breakdown Voltage*, BV).

#### 1.4 Transistores NMOS de drenador extendido.

En muchas de las aplicaciones que existen en la actualidad y que demandan el manejo de altos voltajes es preferible hacer el procesamiento de las señales en voltaje bajo. Aplicaciones como estas pueden ser encontradas en la robótica, en la industria automotriz o en el control de pantallas planas. De esta manera el procesamiento de las señales se realiza en bajos voltajes, o voltajes nominales, para después ser llevados a niveles superiores, a través de dispositivos que sean capaces de servir de interfase entre estos dos niveles.

Generalmente, los voltajes nominales para la tecnología CMOS estándar se encuentran en el orden de 1 a 5 V, entendiéndose así que cualquier voltaje que supere estos rangos puede ser considerado como alto voltaje (HV). Como se mencionó en la sección anterior, las bondades de la tecnología CMOS, hacen que esta sea superior en cierta forma (integración, costo, capacidad de producción, acceso) a muchas de las tecnologías dedicadas.

Una aproximación para poder resolver el problema de la compatibilidad, es el diseño de los llamados transistores de drenador extendido (XD, Extended Drain) o extensión de voltaje inteligente (SVX, Smart Voltage Extension) que pueden ser fabricados en la tecnología CMOS estándar sin la necesidad de incluir máscaras o procesos extras [8]; simplemente haciendo un par de modificaciones en el layout del dispositivo que finalmente ayudaran a aumentar el voltaje de ruptura.

#### 1.5 Organización de la tesis.

La forma en que esta organizada este trabajo es la siguiente:

En el Capítulo 2 se definen y analizan las características generales de las distintas clases de amplificadores de potencia, sus conceptos básicos tales como eficiencia, linealidad, eficiencia añadida, ganancia; además se hace una comparación de todos ellos resaltando sus características de eficiencia, para finalmente resaltar el amplificador clase E como el idóneo para la aplicación propuesta en este trabajo.

El Capítulo 3 se centra en el AP clase E. Se hace una revisión de sus características y funcionamiento comenzando con un diseño idealizado para las especificaciones propuestas, para después hacer un análisis de todas las no idealidades y poder obtener el tamaño de los

transistores, tanto para alto como bajo voltaje. Así mismo, se presentan los resultados finales de dicho diseño.

En el Capítulo 4 se comenzará con un repaso de las limitaciones de la tecnología CMOS en cuanto a voltaje se refiere, así mismo se hará una estimación de los parámetros de la tecnología para dar paso al análisis y diseño de transistores de alto voltaje NMOS o también llamado NMOS de drenaje extendido (XDNMOS) en tecnología CMOS estándar. Se continuará con el diseño del layout y fabricación del dispositivo que sea capaz de tener las características deseadas (alto BV y baja resistencia de encendido) para operar como el conmutador del AP clase E. Finalmente, se presentará una comparación entre los resultados simulados y los resultados obtenidos en la medición.

Por último, en el Capítulo 5 se presentarán las conclusiones y el trabajo futuro a desarrollar, en base a los resultados obtenidos.

#### Referencias.

[1] Lawrence E. Larson, "Integrated Circuit Technology Options for RFIC's—Present Status and Future Directions", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 33, NO. 3, MARCH 1998 387.

- [2] David M. Binkley, James M. Rochelle, Brian K. Swann, Lloyd G. Clonts and Rhonda N. Goble, "A Micropower CMOS, Direct-Conversion, VLF Receiver Chip for Magnetic-Field Wireless Applications", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 33, NO. 3, MARCH 1998.

- [3] R. Sekhar Narayanaswami, "The Design Of A 1.9GHz 250mW CMOS Power Amplifier For DECT", Tesis.

- [4] Nathan O. Sokal and Alan D. Soka, l "Class E-A New Class of High-Efficiency Tuned Single-Ended Switching Power Amplifiers" IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. SC-10, NO. 3, JUNE 1975.

- [5] Siegmund M. Redl, Matthias K. Weber, Malcolm W. Oliphant: "GSM and Personal Communications Handbook", Artech House, May 1998, ISBN-13: 978-089006.

- [6] Troels Emil Kolding, "Review of RF CMOS Performance and Future Process Innovations", Technical Report R98-1014 ISSN 0908-1224 October 8, 1998.

- [7] Edward Spears, Scott Martin, Kerry Burger and David Ngo, "Power amplifier design for portable applications", RF Micro Devices.

- [8] Juan Isdriel Urias Meza, "Transistor de Alto Voltaje en Tecnología CMOS estándar", Tesis.

## Capítulo 2

### Amplificadores de potencia en RF.

LCANZAR la mayor potencia de salida con la máxima eficiencia posible, tratando de obtener alta linealidad es el reto de los diseñadores de AP. En este capítulo se hace un breve repaso por los distintos tipos de amplificadores que existen para finalmente resaltar las características del amplificador de potencia clase E como las idóneas para cubrir las expectativas de la aplicación propuesta.

#### 2.1 Conceptos básicos.

Para poder hacer un estudio detallado de las distintas clases de los amplificadores de potencia, es necesario contar con una serie de conceptos propios del tema. Por principio, será necesario definir con claridad, la diferencia entre un amplificador de pequeña señal y un AP, pues muchas veces esta discrepancia entre uno y otro no es del todo clara.

## 2.1.1 Diferencia entre un amplificador de potencia y un amplificador de pequeña señal.

En los amplificadores existe un compromiso entre linealidad y eficiencia, dos características principales las cuales serán definidas con exactitud posteriormente en este capítulo. Sin embargo, mientras que en los AP se busca optimizar la capacidad de potencia entregada a la carga, así como la eficiencia del mismo aun a costa de su linealidad, en los amplificadores de

pequeña señal sucede lo contrario: la linealidad es el parámetro a optimizar a costa de la eficiencia [1], por lo que generalmente un amplificador de pequeñas señal exhibirá mayor linealidad que un AP, pero a su vez, estos últimos tendrán una eficiencia mayor.

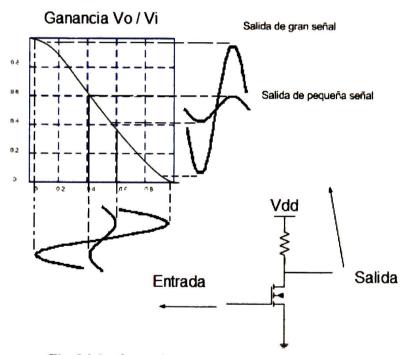

Para observar esto con mayor claridad, veamos el siguiente ejemplo. En la Figura 2.1 se puede observar la configuración de un amplificador en fuente común con las características DC del transistor NMOS y sus formas de onda asociadas. Es claro en la figura como la entrada de pequeñas señal es obtenida a la salida con la misma forma, es decir, sin ser distorsionada pues se mantiene dentro de la región de saturación del transistor; sin embargo por esta misma razón, la potencia que pudiera liberar a la carga es baja. Por otro lado podemos observar que la entrada de gran señal llega a alcanzar las regiones de corte y ohmica o lineal del transistor, por lo que a la salida se aprecia una pequeña distorsión en las crestas de la señal, sin embargo la potencia que puede alcanzar será mayor.

Fig. 2.1 Configuración de un amplificador en fuente común.

Una vez dejando en claro el concepto de AP, se pasará a definir los conceptos básicos.

#### 2.1.2 Eficiencia (Eff).

También conocida como Eficiencia de drenador (DE), la eficiencia es una de las características principales de los amplificadores y es una medida de que tan bien es convertida la potencia de DC proporcionada por la fuente a potencia RF en la carga. Matemáticamente tenemos que:

$$Eff = DE = \eta = \frac{P_{OUT,RF}}{P_{DC}}$$

(2.1)

donde  $P_{OUT,RF}$  es la potencia de salida entregada a la carga y  $P_{DC}$  es la potencia entregada por la fuente de DC.

#### 2.1.3 Ganancia (G).

La ganancia describe la conversión de potencia de RF en la entrada a potencia de RF en la salida, es decir, que tanto aumenta la potencia de RF en el amplificador. La ganancia se puede obtener de la siguiente manera:

$$G = \frac{P_{OUT,RF}}{P_{IN,RF}} \tag{2.2}$$

En este caso P<sub>INRE</sub> es la señal de radio-frecuencia de entrada al amplificador.

#### 2.1.4 Eficiencia de Potencia añadida (PAE, Power Added Efficiency).

La eficiencia de la potencia añadida es un concepto alternativo en los amplificadores, que sin embargo, puede llegar a ser de gran importancia si tomamos en cuenta que la potencia que se disipa en la entrada del transistor es incluida en este parámetro; en muchas ocasiones la potencia de entrada que es proporcionada por una etapa anterior (generalmente conocida como driver) se desprecia, pero ésta puede llegar a ser grande debido al gran tamaño de los transistores y aun más si se trabaja en RF, lo que implica tener un desperdicio de energía y posiblemente problemas para suministrar esta potencia; por esta razón es de suma importancia contar con una buen PAE para esta aplicación. Su definición matemática es:

$$PAE = \frac{P_{OUT,RF} - P_{IN,RF}}{P_{DC}} \tag{2.3}$$

#### 2.1.5 Linealidad.

Como se mencionó en la Sección 2.1.1, la linealidad es otro de los conceptos básicos en los amplificadores, que sin embargo en algunas aplicaciones de potencia, llega a perder valor, pues debido al tipo de modulación no es necesario que la señal de salida tenga la forma de la señal de entrada. Debido a que la aplicación aquí propuesta es una de las que no requieren gran linealidad, simplemente será mencionado que existen dos conceptos que permiten estimar la linealidad: La distorsión armónica central y la "compresión de la ganancia" Más detalles pueden ser consultados en [1] [2].

#### 2.2 Tipos de amplificadores.

Existen principalmente dos tipos de amplificadores dependiendo de la región en que opere el dispositivo activo de estos (generalmente un transistor): amplificadores de potencia en modo fuente de corriente y amplificadores de potencia en forma conmutada. A su vez, ambos pueden subdividirse en diferentes clases según la forma de operación. A continuación se hace una descripción detallada de estos.

#### 2.2.1 Amplificadores de potencia en Modo Fuente de Corriente.

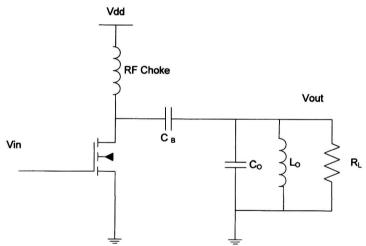

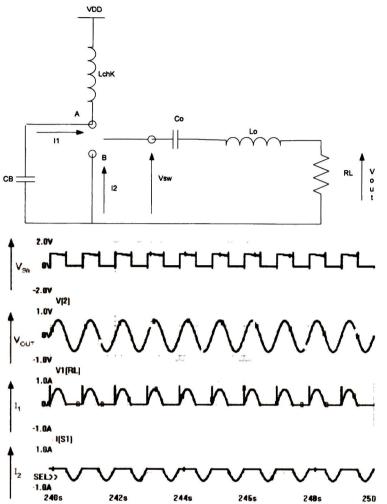

Estos amplificadores están caracterizados porque el transistor (asumiendo que es un FET) trabaja en la región de corte y saturación. La Figura 2.2 muestra la configuración básica de este tipo de amplificadores. La configuración de fuente común que se presenta en la figura es la más usual puesto que es la que permite tener una máxima eficiencia. Como podemos apreciar en la figura, el drenador se conecta a la alimentación a través de un inductor llamado de Choque (RF *Choke*) el cual actúa idealmente como una fuente de corriente, presentando una resistencia teóricamente infinita para la frecuencia de operación. Además en el circuito se tiene un capacitor llamado de bloqueo (C<sub>R</sub>) que elimina cualquier nivel de DC a la salida, y un circuito resonante (C<sub>O</sub>, L<sub>O</sub>) que permitirá filtrar la señal de salida hacia la carga; en este caso descrito se trata de un circuito tanque.

Fig. 2.2. Configuración básica de los amplificadores de potencia en modo fuente de corriente.

Las clases de amplificadores que se encuentran dentro de esta categoría son: el clase A, el clase B, el clase AB y el clase C; estos amplificadores difieren únicamente como veremos a continuación, en el punto en que se encuentra operando el transistor, y por lo tanto, en el ángulo de conducción, el cual puede ser definido matemáticamente como:

$$Angulo.de.Conduccion = 360^{\circ} \left(\frac{T_{ON}}{T_{RF}}\right)$$

(2.4)

donde  $T_{\text{ON}}$  es el tiempo durante el cual el transistor se encuentra conduciendo y  $T_{\text{RF}}$  se refiere al periodo de la señal de RF de entrada.

#### Amplificador de potencia clase A.

También muchas veces llamado amplificador lineal, esta clase se caracteriza por conducir durante los 360°, es decir, el transistor se encuentra encendido en todo el ciclo de entrada. Sin embargo, es importante mencionar que no por esta razón, este tipo de amplificador deja de presentar no-linealidades, pues como ya vimos en la sección anterior, el hecho de que la señal de entrada pueda superar la región de saturación provoca una distorsión en la forma de onda de la salida, lo que idealmente no debería de suceder en este tipo de amplificadores. Sus formas de onda características se muestran en la Figura 2.3.

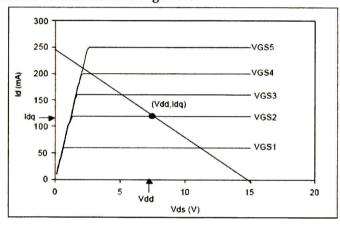

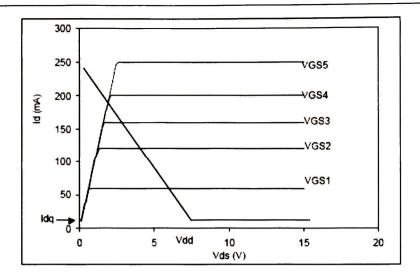

Fig. 2.3 Línea de carga y forma de onda de la corriente de salida para un amplificador clase A.

Debido a su característica, y como era de esperarse, esta clase de amplificador es el que en teoría presenta una menor eficiencia en comparación con los demás, pues su potencia de salida en el mejor de los casos, cuando el voltaje del drenador vaya de 0 a 2V<sub>DD</sub>, será igual a:

$$P_{OUT} = \frac{V_{DD}^2}{2R_I} \tag{2.5}$$

y a su vez la potencia de DC consumida será igual a:

$$P_{DC} = V_{DD}I_{DD} = \frac{V_{DD}^2}{R_I}$$

(2.6)

Por lo tanto, remitiéndonos a la definición matemática antes descrita para la eficiencia y sustituyendo la ecuación 2.5 y 2.6 en ésta, tenemos que:

$$Eff = \frac{P_{OUT}}{P_{DC}} = \frac{\frac{V_{DD}^2}{2R_L}}{\frac{V_{DD}^2}{R_L}} = \frac{1}{2}$$

(2.7)

Así, teóricamente la mayor eficiencia que se puede lograr para este tipo de AP será del 50%.

#### Amplificador de potencia clase B.

Como vimos en la sección anterior, el hecho de que el AP clase A conduzca todo el tiempo, hace que sea poco eficiente. Así, una manera de incrementar la eficiencia sería disminuyendo el ángulo de conducción. El amplificador de potencia clase B, es un tipo de amplificador que tiene la misma configuración que se mostró en la Figura 2.2, sin embargo el transistor conducirá solo la mitad del ciclo completo de RF, haciendo que la eficiencia aumente. Como era de esperarse también el número de frecuencias indeseadas, es decir aquellas que no son la frecuencia a la que debería trabajar el amplificador, aumentarán; sin embargo el circuito tanque se encargara de filtrar la frecuencia fundamental. Sus formas de onda puede observarse en la Figura 2.4.

Ahora se procederá a obtener la Eficiencia teórica del amplificador clase B, tal como lo hicimos para el AP clase A. La potencia de salida en el mejor de los casos al igual que en el AP clase A será:

$$P_{OUT} = \frac{V_{DD}^2}{2R_I} \tag{2.8}$$

Fig. 2.4 Línea de carga y forma de onda de la corriente de salida para un amplificador clase B.

Sin embargo la potencia de DC será diferente y se puede obtener calculando el promedio de un ciclo de RF. Así

$$P_{DC} = V_{DD}I_{DC} \tag{2.9}$$

donde

$$I_{DC} = \frac{1}{T_{RF}} \int_{0}^{T_{RF}/2} sen\left(\frac{2\pi}{T_{RF}}t\right) dt = \frac{2}{\pi} \frac{V_{DD}}{R_{L}}$$

(2.10)

por lo tanto sustituyendo la ecuación 2.10 en la ecuación 2.9 tenemos

$$P_{DC} = \frac{2}{\pi} \frac{V_{DD}^2}{R_I} \tag{2.11}$$

entonces la Eficiencia será:

$$Eff = \frac{P_{OUT}}{P_{DC}} = \frac{\frac{V_{DD}^2}{2R_L}}{\frac{2V_{DD}^2}{\pi R_L}} = \frac{\pi}{4} \approx 0.785$$

(2.12)

Así este tipo de amplificador exhibe teóricamente una Eficiencia cercana al 80%.

#### Amplificador de potencia clase AB.

En ciertas aplicaciones es necesario contar con un amplificador capaz de tener una mayor eficiencia que el amplificador clase A pero que además ofrezca mejor linealidad que el amplificador clase B. Así inmediatamente la solución que salta a la vista es hacer que el transistor conduzca en un punto entre  $180^{\circ}$  ( $\pi$ ) y  $360^{\circ}$  ( $\pi$ ). A este tipo de amplificado se le conoce como clase AB. Como era de esperarse su eficiencia, en teoría, estará entre 0.5 y 0.785 dependiendo del ángulo de conducción.

#### Amplificador de potencia clase C.

Algunas veces, y sobre todo en aplicaciones de RF, no es necesario contar con amplificadores que exhiban gran linealidad, puesto que se utilizan otros tipos de modulación. Sin embargo estas aplicaciones requieren tener mayor eficiencia que la que puede alcanzarse con un amplificador clase B. Así pues, el amplificador clase C cumple con estas especificaciones ya que su ángulo de conducción es menor a 180° En la Figura 2.5 se puede observar sus formas de onda.

Su eficiencia máxima estará determinada precisamente por el tiempo en que el transistor se encuentre conduciendo y teóricamente estará dada por la siguiente expresión:

$$Eff = \frac{2y - sen(2y)}{4(sen(y) - y\cos(y))}$$

(2.13)

donde el parámetro y corresponde al ángulo de conducción expresado como un porcentaje del periodo de RF.

Así mismo la potencia que podrá proporcionar con esta eficiencia será:

$$P_{OUT} = \frac{2y - sen(2y)}{8\pi(1 - \cos(y))}$$

(2.14)

Como se puede notar la eficiencia puede ser incrementada disminuyendo el ángulo de conducción, sin embargo la capacidad de potencia de salida se vera disminuida hasta llegar a cero.

Fig. 2.5 Línea de carga y forma de onda de la corriente de salida para un amplificador clase C.

#### 2.2.2 Amplificadores de potencia en Modo Conmutado.

Una de las limitantes de los amplificadores de potencia en modo fuente de corriente es que incluso teóricamente no pueden alcanzar una eficiencia del 100%. Por esta razón surgieron los amplificadores en forma conmutada que tienen como principal característica el uso del

transistor como un conmutador o switch. Así, con condiciones ideales en el transistor, es decir una resistencia de encendido igual a cero, una resistencia infinita en estado apagado y tiempos de subida y bajada de la señal nulos, es posible alcanzar la eficiencia teórica del 100%.

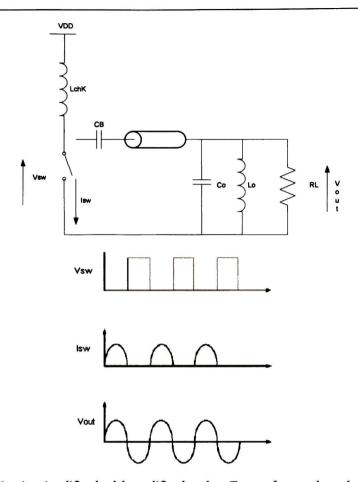

En esta sección se hará un repaso de los amplificadores de potencia clase D y clase F. El amplificador de potencia clase E, al ser el tema principal en este trabajo, será analizado con mayor detalle en el siguiente capítulo. Pero antes, será conveniente detallar un par de conceptos básicos en este tipo de amplificadores: la conmutación suave y la conmutación rígida.

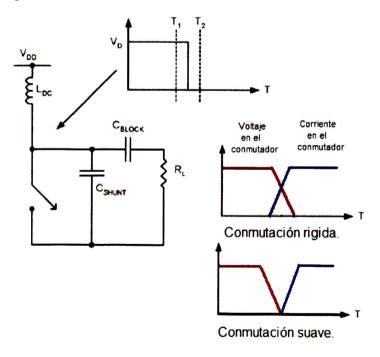

#### Conmutación Suave y Conmutación rígida.

Para entender mejor el concepto de conmutación suave y conmutación rígida será necesario remitirnos a la Figura 2.6. En esta figura podemos observar el circuito simplificado de un amplificador de conmutación; se asume que el conmutador para este circuito es ideal, es decir presenta las características mencionadas en la Sección 2.2.2. Así, si el conmutador se cierra en el tiempo T1, la energía almacenada en el capacitor  $C_{SHUNT}$  será desperdiciada puesto que quedará cortocircuitado a tierra, provocando un traslape entre la corriente y voltaje en el conmutador como se observa en la figura. Por lo tanto, aunque se tenga un conmutador ideal, incluso teóricamente la eficiencia no será del 100%. A esta condición se le conoce como conmutación rígida.

Fig. 2.6 Diagrama simplificado de un amplificador conmutado para simplificar la diferencia entre conmutación suave y conmutación rígida.

Por otro lado, si el conmutador es cerrado en el tiempo T2, el capacitor habrá entregado toda su energía almacenada a la carga, lo que evitará el traslape entre corriente y voltaje en el conmutador y por lo tanto, permitirá tener en teoría una eficiencia del 100%. A esta condición se le conoce como conmutación suave.

#### Amplificador de potencia clase D.

Algunas veces, y sobre todo en aplicaciones de RF, no es necesario contar con amplificadores que exhiban gran linealidad, puesto que se utilizan otros tipos de modulación. Sin embargo estas aplicaciones requieren tener mayor eficiencia que la que puede alcanzarse con un amplificador clase B. Así pues, el amplificador clase C cumple con estas especificaciones ya que su ángulo de conducción es menor a 180° En la Figura 2.5 se puede observar sus formas de onda.

En la Figura 2.7 se puede observar la implementación básica de un amplificador clase D. Así mismo, la figura muestra las formas de onda asociadas a este tipo de amplificador.

El funcionamiento de este tipo de amplificador a grandes rasgos es como sigue: la inductancia L<sub>chk</sub>, al igual que en los amplificadores de la sección anterior, funciona como una fuente de corriente. El transistor conmuta del punto entre el punto A y el punto B, con un ciclo de trabajo del 50%. La carga esta conectada a través de un circuito serie resonante entonado a la frecuencia de operación. Debido a esto, podemos ver que la corriente de salida será una señal sinusoidal [3].

Fig. 2.7 Circuito simplificado del amplificador clase D y sus formas de onda asociadas.

## Amplificador de potencia clase F.

En la Figura 2.8 podemos observar el circuito básico de un amplificador de potencia clase F, así como sus formas de onda asociadas. El funcionamiento de este tipo de amplificador considerando un conmutador ideal, es como sigue: la red de carga de este amplificador consiste en una línea de transmisión de ¼ de onda, y el circuito resonante en paralelo RLC que se encuentra entonado a la frecuencia fundamental.

Fig. 2.8 Circuito simplificado del amplificador clase F y sus formas de onda asociadas.

### 2.2 Conclusiones.

Cabe señalar que debido a sus características de eficiencia, los amplificadores en forma de fuente de corriente fueron descartados para ser utilizados en la aplicación propuesta en esta tesis. Por otro lado, el amplificador clase D, debido a sus características de conmutación rígida, esta limitado a frecuencias de RF bajas (menores a 150 MHz en la mayoría de los casos) por lo que también se descartó para ser utilizado en este sistema de 900 MHz. Así los amplificadores clase E y F son los ideales para cubrir las especificaciones propuestas. Sin embargo, hay dos aspectos que resaltan al amplificador clase E sobre el amplificador clase F: primero, el amplificador clase E puede ser implementado más fácilmente ya que es más sencillo que el amplificador clase F; y segundo, el hecho de contar con mayor literatura para implementar exitosamente el AP clase E en tecnología CMOS. Estos dos puntos fueron los que finalmente contribuyeron para que el AP clase E fuera seleccionado para implementar la aplicación propuesta.

## Referencias.

[1] Stephen Christopher Ferry, "Development of a High-Efficiency, Low-Power RF Power Amplifier for Use in a High-Temperature Environment", Tesis.

- [2] Walt Kester, "Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor", Analog Devices.

- [3] Abulet Mihai, "RF power amplifiers", ISBN 1-884932-12-6.

# Capítulo 3

# El amplificador de potencia clase E.

AS aplicaciones actuales de comunicación móvil demandan altas eficiencias de energía para tener un mayor rendimiento en las baterías. Parte fundamental en un sistema de comunicación son los amplificadores de potencia, responsables en gran medida del consumo de energía. Para obtener alta eficiencia en un amplificador de potencia se requiere de topologías de conmutación suave, es decir aquellas en las que las condiciones de voltaje y corriente en el conmutador no coinciden en el tiempo.

Sin embargo, el uso de un transistor como dispositivo de conmutación, requiere también de cierta potencia de entrada para la saturación del mismo, y esta potencia se incrementa considerablemente cuando se trabaja en RF, pues como es bien sabido a frecuencias altas las componentes parásitas del transistor usado como conmutador, tendrán un mayor peso. Un parámetro importante para medir esta demanda de potencia en la entrada es la Eficiencia de Potencia Añadida (PAE).

En el presente capítulo se establece el concepto del funcionamiento del amplificador de potencia clase E, perteneciente al tipo de amplificadores conmutados que tiene la posibilidad de trabajar en RF con una alta eficiencia. Se propondrá una metodología de diseño en base al dimensionamiento del transistor y consecuentemente a su resistencia de encendido (Ron) que permita obtener una alta eficiencia al igual que un alto porcentaje de PAE. Así mismo se verán las ventajas de utilizar un mayor voltaje de alimentación en el circuito, lo cual llevara a proponer el uso de dispositivos que cuenten con un mayor voltaje de ruptura.

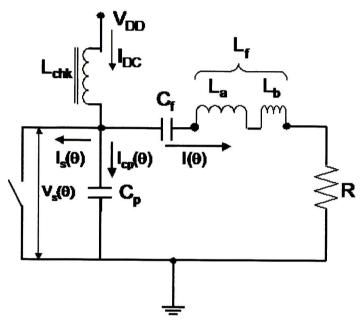

## 3.1 El funcionamiento del amplificador de potencia clase E.

Para comenzar el análisis del AP clase E se supondrá condiciones ideales, es decir una resistencia de encendido en el conmutador (Ron) igual a cero y una resistencia infinita cuando el conmutador esta apagado. Se considerara también tiempos de encendido y apagado nulos, así como cero demanda de la potencia de entrada y un ciclo de trabajo del conmutador del 50%. En la Figura 3.1 podemos observar el diagrama eléctrico idealizado del AP clase E.

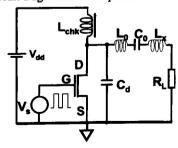

Fig. 3.1 Modelo eléctrico de un amplificador clase E ideal.

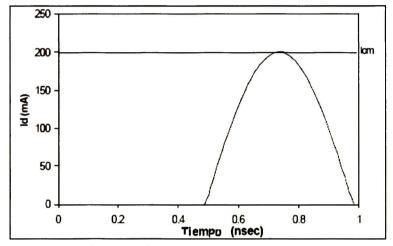

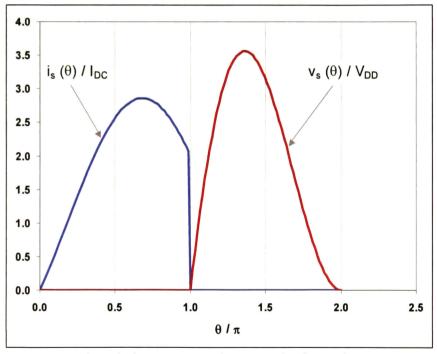

Las condiciones deseadas de un amplificador clase E ideal para alcanzar una eficiencia teórica del 100% son la no-coincidencia en el tiempo de la corriente  $I_s(\theta)$  y voltaje  $V_s(\theta)$  en el conmutador, así como un voltaje cero con una pendiente nula cuando el conmutador se cierra. La gráfica de la Figura 3.2 ilustra las formas de onda ideales para el voltaje y la corriente en el conmutador normalizadas.

Cuando el conmutador está cerrado el voltaje en el mismo será igual a cero y la corriente a través del conmutador es la suma de la corriente sinusoidal de salida,  $I(\theta)$  y la corriente  $I_{DC}$  constante de la fuente de voltaje  $V_{DD}$ . Cuando el conmutador está abierto no habrá corriente circulando por el conmutador, mientras que el voltaje  $V_S(\theta)$  será igual a la corriente que carga al capacitor por la reactancia en el mismo, esto es:

$$\begin{split} &i_{\mathrm{s}}(\theta) = I_{\mathrm{dc}}(1 + \frac{\pi}{2} \operatorname{sen}\theta - \cos\theta) & (0 < \theta \leq \pi) \\ &v_{\mathrm{e}}(\theta) = \frac{I_{\mathrm{dc}}}{\omega C_{\mathrm{p}}} (\theta - \frac{3\pi}{2} - \frac{\pi}{2} \cos\theta - \sin\theta) & (\pi < \theta \leq 2\pi) & (1) \\ &i_{\mathrm{s}}(\theta) = 0, \ (\pi < \theta \leq 2\pi) & v_{\mathrm{e}}(\theta) = 0, \ (0 < \theta \leq \pi) \end{split}$$

El conmutador opera a la frecuencia

$$\omega = 1/\sqrt{L_{\bullet}C} \tag{3.3}$$

de tal manera que la reactancia de la inductancia en exceso,  $L_b$ , causa que  $V_s(\theta)$  retorne a cero con una pendiente igual a cero antes de que el conmutador se cierre [1].

Fig. 3.2 Formas de onda de corriente y voltaje normalizadas en el conmutador de un amplificador clase E.

De las condiciones de corriente de Kirchoff en el nodo no aterrizado del conmutador, se obtienen las ecuaciones de conmutación necesarias para cumplir con las condiciones deseadas de un amplificador clase E ideal. De estas ecuaciones puede encontrarse el ángulo de fase necesario a proveer por el circuito entonado de carga, así como los valores del máximo voltaje en el conmutador y la máxima corriente en el mismo.

Tomando como variables independientes la frecuencia de operación (f), la potencia de salida deseada  $(P_{OUT})$  y el factor de calidad del circuito resonante  $(Q_i)$ , se puede calcular los parámetros de la red de carga del amplificador en función de las ecuaciones de conmutación, empleando el método de análisis de Fourier del voltaje en el conmutador.

En las Tablas 3.1, 3.2, 3.3, se muestra un resumen de las ecuaciones más importantes de un amplificador clase E utilizando un conmutador ideal con el 50% de ciclo de trabajo [2], [3].

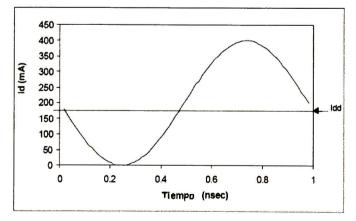

Un punto importante a resaltar es que la corriente máxima en el conmutador del amplificador clase E, es alrededor de tres veces su corriente promedio y su voltaje máximo del orden de 3.5 veces el voltaje de alimentación (Fig. 3.2).

Puesto que se propone el uso de un N-MOSFET como dispositivo de conmutación, para el primer caso debe cuidarse que el transistor tenga la capacidad de proporcionar la corriente demandada y en el segundo, el transistor debe de contar con un voltaje de ruptura adecuado. Dado que los voltajes de ruptura de los actuales transistores MOSFET en la escala de submicrones, tienen un relativamente bajo voltaje de ruptura, para este tipo de aplicaciones será conveniente encontrar un diseño que permita incrementar su voltaje de ruptura o usar topologías de diseño adecuadas como se verá en el siguiente capítulo.

El modelo de conmutador ideal es adecuado para describir el comportamiento global del amplificador, siempre y cuando los efectos parásitos sean despreciables.

| Corriente en el conmutador en el intervalo $0 < \theta \le \pi$                                                                                                         | $i_{s}(\theta) = I_{DC}[1 + \frac{\pi}{2\text{sen}\phi} \text{sen}(\theta + \phi)]$ $i_{s}(\theta) = I_{DC}[1 + \frac{\pi}{2} \text{sen}(\theta) - \cos(\theta)]$                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltaje en el conmutador en el intervalo $\pi < \theta \leq 2\pi$                                                                                                       | $\begin{aligned} \mathbf{V_s}(\theta) &= \pi \mathbf{V_{DD}} \{ (\theta - \phi) - \frac{\pi}{2 \cos \phi} [\cos(\theta + \phi) + \cos \phi] \} \\ \mathbf{V_s}(\theta) &= \pi \mathbf{V_{DD}} [\theta - \frac{3\pi}{2} - \frac{\pi}{2 \cos \phi} \cos \theta - \sin \theta] \end{aligned}$ |

| Angulo de fase $\phi$ para cumplir con las condiciones nominales: $v_{\alpha}(\theta) = 0 \text{ y } \frac{dv_{\alpha}(\theta)}{d\theta} = 0 \text{ en } \theta = 2\pi$ | $\phi = \arctan(-\frac{2}{\pi}) + n\pi$                                                                                                                                                                                                                                                    |

| Amplitud de la corriente senoidal en la carga                                                                                                                           | $I_{m} = -\frac{\pi}{2\cos\phi}I_{DC}$ $I_{m} = -\frac{\pi P_{R}}{2V_{DD}\cos\phi}$                                                                                                                                                                                                        |

| Amplitud del voltaje senoidal en la carga                                                                                                                               | $V_{RM} = -\frac{4V_{DD}\cos\phi}{V_{RM}} = \frac{2P_{R}}{I_{m}}^{\pi}$                                                                                                                                                                                                                    |

| Intensidad de la componente de corriente directa                                                                                                                        | $I_{DC} = \pi \omega C_{p} V_{DD}$ $I_{DC} = \frac{P_{R}}{V_{DD}}$                                                                                                                                                                                                                         |

| Corriente maxima en el conmutador                                                                                                                                       | $\begin{aligned} \textbf{I}_{\text{sm}} &= \textbf{I}_{\text{DC}} + \textbf{I}_{\text{m}} \\ \\ \text{para}  \theta'' &= \omega \textbf{t}_{\textbf{L}_{\text{m}}} = \frac{3\pi}{2} - \phi \end{aligned}$                                                                                  |

| Voltaje maximo en el conmutador                                                                                                                                         | $V_{sm} = \pi V_{DD}(\theta' - \pi)$ $donde \ \theta' = \omega t_{V_{sm}} = arcsen(-\frac{2\cos\phi}{\pi}) - \phi + 2\pi$                                                                                                                                                                  |

Tabla 3.1 Resumen de ecuaciones que describen el comportamiento de un amplificador clase E, usando condiciones ideales y un ciclo de trabajo del 50%.

| Resistencia de carga                                                                                                    | $R = \frac{8}{\pi^2} \frac{V_{00}^2 \cos^2 \phi}{P_R}$                               |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Capacitancia en paralelo con el conmutador                                                                              | $C_p = \frac{P_R}{\pi \omega V_{0D}^2}$                                              |

| Inductancia total del circuito resonante                                                                                | $L_r = \frac{Q_L R}{\omega}$                                                         |

| Capacitancia del circuito resonante                                                                                     | $C_{t} = \frac{1}{\omega^{2}(L - L_{b})}$                                            |

| Inductancia necesaria para proveer el<br>angulo de fase necesario para la operación<br>nominal del amplificador clase E | $L_b = \frac{R}{\varpi} \frac{[(1/8)\pi^2 - \cos^2 \phi}{-\text{sen}\phi \cos \phi}$ |

**Tabla 3.2** Resumen de ecuaciones que describen el valor de las componentes discretas de un AP Clase E. Condiciones ideales y un ciclo de trabajo del 50 %.

| Resistencia de carga                                                                                                    | $R = 0.5768 \frac{V_{DD}^2}{P_R}$                                                             |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Capacitancia en paralelo con el conmutador                                                                              | $C_p = 0.318 \frac{P_R}{\omega V_{DD}^2}$                                                     |

| Inductancia necesaria para proveer el<br>angulo de fase necesario para la operación<br>nominal del amplificador clase E | $L_b = 1.1525 \frac{R}{\varpi}$                                                               |

| Corriente maxima en el conmutador                                                                                       | $I_{um} = \frac{P_R}{V_{DD}} [1 - \frac{\pi}{2\cos\phi}]$ $I_{um} = 2.862 \frac{P_R}{V_{DD}}$ |

| Voltaje maximo en el conmutador                                                                                         | $V_{em} = 3.553 V_{DD}$                                                                       |

| Tiempo para V <sub>am</sub>                                                                                             | θ' = 1.36 π rad                                                                               |

| Tiempo para l <sub>am</sub>                                                                                             | θ" = 2.138 rad                                                                                |

| Amplitud de la corriente senoidal en la carga                                                                           | $I_m = 1.862 \frac{P_R}{V_{DD}}$ $I_m = 1.862 I_{DC}$                                         |

| Amplitud del voltaje senoidal en la carga                                                                               | V <sub>RM</sub> = 1.074 V <sub>DO</sub>                                                       |

**Tabla 3.3** Resumen de ecuaciones que describen el valor de las componentes discretas de un AP clase E incluyendo el valor del ángulo de fase φ. Condiciones ideales y un ciclo de trabajo del 50 %.

## 3.2 Diseño de un amplificador de potencia clase E Ideal.