BC-651 Don.-2011

xx (179121.1)

#### Centro de Investigación y de Estudios Avanzados del Instituto Politécnico Nacional Unidad Guadalajara

# Topologías del DVR basadas en un convertidor matricial para mejorar la calidad de la energía en sistemas de distribución

Tesis que presenta:

José Merced Lozano García

para obtener el grado de: **Doctor en Ciencias**

en la especialidad de: Ingeniería Eléctrica

Director de Tesis

Dr. Juan Manuel Ramírez Arredondo

CINVESTAV del IPN Unidad Guadalajara, Guadalajara, Jalisco, Febrero de 2011.

CLASIF: TK165.48 469 2011 ADQUIS... FC - 651 FECHA: 18 - Agosto - 2011 PROCED... Ton. - 2011

10:174541-1001

#### Centro de Investigación y de Estudios Avanzados

#### del Instituto Politécnico Nacional

Unidad Guadalajara

# DVR's Topologies matrix converter-based for improving power quality in distribution systems

A dissertation submitted by: **José Merced Lozano García**

For the degree of: **Doctor of Sciences**

In the specialty of: **Electrical Engineering**

Advisor: **Dr. Juan Manuel Ramírez Arredondo**

CINVESTAV del IPN Unidad Guadalajara, Guadalajara, Jalisco, February 2011

# Topologías del DVR basadas en un convertidor matricial para mejorar la calidad de la energía en sistemas de distribución

#### Tesis de Doctorado en Ciencias Ingeniería Eléctrica

#### Por:

#### José Merced Lozano García

Maestro en ciencias en Ingeniería Eléctrica Centro de Investigación y de Estudios Avanzados del I.P.N. Unidad Guadalajara 2003-2005

Becario de CONACYT, expediente no. 203059

Director de Tesis

Dr. Juan Manuel Ramírez Arredondo

CINVESTAV del IPN Unidad Guadalajara, Febrero de 2011

# DVR's Topologies matrix converter-based for improving power quality in distribution systems

# A dissertation for the degree of Doctor of Sciences in Electrical Engineering

#### By:

#### José Merced Lozano García

Master of Sciences in Electrical Engineer Centro de Investigación y de Estudios Avanzados del I.P.N. Unidad Guadalajara 2003-2005

Scholarship by CONACYT, No. 203059

#### Advisor:

Dr. Juan Manuel Ramírez Arredondo

## **Dedicatoria**

A mis padres, Concepción y Raquel, quienes constituyen el mejor ejemplo que pueda seguir, por su amor incondicional e incansable apoyo.

A mis hermanos, por estar siempre cerca, guiándome por el camino correcto y recordándome en todo momento quién soy yo.

## Agradecimientos

A mi familia por su comprensión e incondicional apoyo.

A María G. por estar ahí en todo momento.

Al Dr. Juan Manuel Ramírez Arredondo por la confianza, paciencia y sabiduría que me permitieron llevar a buen término este proyecto.

A mis compañeros y amigos del CINVESTAV, en especial a los borrachines, por los buenos momentos compartidos.

A los investigadores del CINVESTAV por compartir conmigo un poco de su invaluable sabiduría dentro y fuera del ámbito académico.

A todas las personas que laboran en el CINVESTAV Unidad Guadalajara por hacer muy placentera mi estancia en la unidad.

A mis compañeros del Instituto de Tecnología Energética de la Universidad de Aalborg por su apoyo y confianza.

Al Consejo Nacional de Ciencia y Tecnología por el apoyo económico otorgado para la realización del presente proyecto.

A Dios, por permitirme continuar en este camino.

xii

#### Resumen

El objetivo de la presente investigación es desarrollar un esquema de compensación de voltaje novedoso, capaz de mitigar algunos de los problemas más comunes concernientes a la calidad de energía en los sistemas eléctricos de distribución. Los disturbios suscitados en las redes de suministro de energía provocan variaciones en los perfiles de voltaje a lo largo del sistema especialmente en los nodos cercanos a la falla. Por otro lado, el incremento en la utilización de sistemas industriales automatizados, la conexión de fuentes convertidores basadas en electrónica de potencia, etc., generan una gran cantidad de componentes armónicos contaminando el sistema eléctrico. Estos eventos deterioran el rendimiento de equipos convencionales, ocasionan fallas en líneas de producción, provocan la desconexión de un gran número de usuarios y causan grandes pérdidas económicas en general.

Con el propósito de compensar tales condiciones adversas en el voltaje, en este trabajo de tesis se proponen dos nueva topologías para un Restaurador Dinámico de Voltaje (DVR) basadas en el convertidor matricial. Los esquemas propuestos incorporan la tecnología de la conversión de energía CA-CA y adquieren del sistema la energía de compensación requerida, lo que permite eliminar las desventajas que supone el uso de un enlace de CD y la necesidad de elementos de almacenamiento. La topología convencional del DVR se utilizada para generar los voltajes de compensación durante condiciones que involucran variaciones de voltaje balanceadas y desbalanceadas, además de voltajes distorsionados en el sistema. En la segunda topología, los voltajes de compensación se inyectan en el lado del sistema de suministro. Esta configuración permite que se mantenga un voltaje constante en las terminales de entrada del convertidor, resultando en una solución eficiente para la compensación de variaciones pronunciadas en el voltaje.

El control el DVR se logra mediante la combinación de un controlador feed-back / feed-forward y la estrategia de modulación propuesta, Modulación Directa en el Espacio Vectorial Modificada (MDSVM), desarrollada para generar los voltajes de compensación a través del convertidor matricial.

La implementación experimental del convertidor matricial está basada en interruptores de estado sólido IGBTs y el control se programó en un Procesador Digital de Señales (DSP). Se llevaron a cabo simulaciones numéricas en el programa PSCAD para validar las topologías propuestas, y además se presentan los resultados experimentales obtenidos a fin de confirmar el esquema de control.

#### **Abstract**

The objective of this research is to develop a novel voltage compensation scheme that can be able to cope with common power quality problems presented in power distribution systems. Disturbances occurring in the supply power networks or facilities in plants can cause variations in voltages profile throughout the system, especially in the nodes located close to the fault. On the other hand, the increasing use of industrial systems microprocessor-based, utility line-connected solid state power converters, etc., have polluted the power system with harmonic components. These events are reasons for failures in common equipment, tripping of computer-controlled industrial processing lines, power disruption for end users and economic losses in general.

In order to mitigate such voltages conditions, this dissertation proposes two novel DVR topologies based on the matrix converter. The proposed schemes include the AC-AC power conversion technology and acquire from the grid the necessary energy during the disturbance, which eliminates the drawbacks imposed by the use of DC-link passive devices and the need of energy storage components. The conventional DVR topology is used to generate the compensation voltages in conditions that involve balanced and unbalanced variations, and distorted supplied voltages. In the second topology, compensation voltages are injected on the supply-side of the system. This configuration permits to hold a constant input voltage for the converter, resulting in an efficient solution for deep voltage sags.

DVR's control is achieved by the combination of the feed-back / feed-forward controller and the proposed Modified Direct Space Vector Modulation (MDSVM) strategy, developed to generate the compensation voltages through the matrix converter.

The hardware implementation of the matrix converter is based on IGBTs and DSP control. Simulations in PSCAD software have been carried out to verify the validity of the proposed topologies, and prototype experimental results are provided to confirm the control scheme.

# **Contents**

| Ded  | licatoria                                                | ix       |

|------|----------------------------------------------------------|----------|

| Agra | adecimientos                                             | xi       |

| Resi | umen                                                     | xiii     |

| Abst | tract                                                    | χV       |

| Con  | tents                                                    | xvii     |

| List | of Figures                                               | xx       |

|      | of Tables                                                | xxiv     |

| List | of Acronyms                                              | xxv      |

| CH   | APTER 1 Introduction                                     |          |

|      |                                                          |          |

| 1.1  | Introduction and Motivation                              | 1        |

| 1.2  | Justification                                            | 2        |

| 1.3  | Objectives and Contributions                             | 3        |

| 1.4  | Thesis Outline References                                | 4<br>5   |

| 1.5  | References                                               | 3        |

| CH   | APTER II Voltage Disturbances and Mitigation Devices     |          |

| 2.1  | Power quality issues                                     | 7        |

|      | 2.1.1 Voltage disturbances in distribution systems       | 8        |

|      | 2.1.2 Harmonic distortion                                | 10       |

|      | 2.13 Voltage Imbalance                                   | 11       |

| 2.2  | Power quality guidelines and standards                   | 12       |

| 2.3  | Power electronics applications in power systems          | 14       |

|      | 2.31 FACTS Controllers                                   | 14       |

| 2.4  | 2.3.2 Custom Power System (CUPS) devices                 | 15       |

| 2.4  | AC-link Power Converters  2.4.1 Direct AC-AC converters  | 16<br>16 |

|      | 2.42 AC-link converters                                  | 18       |

| 2.5  | Conclusions                                              | 22       |

| 2.6  | References                                               | 22       |

| CH   | APTER III Fundamentals of the Matrix Converter Technolog | y        |

| 3.1  | Background                                               | 27       |

| 3.2  | Introduction to matrix converter technology              | 29       |

| 3.3  | Analysis of Bi-directional power switches                | 31       |

|      |                                                          |          |

| 3.4 | Curren  | t commutation techniques                                          | 32  |

|-----|---------|-------------------------------------------------------------------|-----|

|     | 3.41    | Four step commutation strategy                                    | 34  |

| 3.5 | Modul   | ations Techniques                                                 | 35  |

|     | 3.5.1   | Scalar Algorithms                                                 | 37  |

|     | 3.5.2   | Indirect Modulation                                               | 40  |

|     | 3.5.3   | Space Vector Modulation Methods                                   | 40  |

| 3.6 | Overvo  | oltage protection circuit                                         | 43  |

| 3.7 | Conclu  | sions                                                             | 44  |

| 3.8 | Refere  | nces                                                              | 46  |

| CHA | APTER   | IV Modified DSVM Strategy                                         |     |

| 4.1 | Introdu | action                                                            | 51  |

| 4.2 | Modifi  | ed DSVM to compensate unbalanced and distorted input voltages     | 52  |

|     | 4.2.1   | Unbalanced conditions specification                               | 52  |

|     | 4.2.2   | Switching states analysis in Park's complex space for unbalanced  |     |

|     |         | Conditions                                                        | 56  |

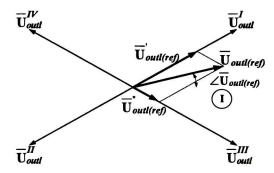

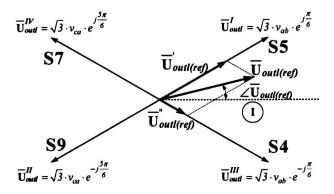

|     | 4.2.3   | Voltage reference tracking                                        | 59  |

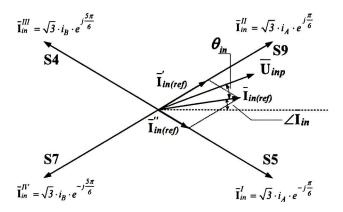

|     | 4.2.4   | Current references tracking                                       | 61  |

|     | 4.2.5   | Duty Cycles computation                                           | 63  |

|     | 4.2.6   | Computation Tables                                                | 65  |

| 4.3 | Matrix  | converter with the modified DSVM simulations                      | 68  |

|     | 4.3.1   | Condition I: Unbalanced Input Voltage                             | 69  |

|     | 4.3.2   | Condition II: Distorted Input Voltage                             | 72  |

| 4.4 | Experi  | mental Results                                                    | 74  |

| 4.5 | Conclu  | sions                                                             | 79  |

| 4.6 | Referei | nces                                                              | 80  |

| CHA | APTER   | V Matrix Converter-Based Voltage Compensator                      |     |

| 5.1 | DVR o   | perational principle                                              | 83  |

| 5.2 | DVR to  | ppologies                                                         | 85  |

|     | 5.2.1   | DC-link based DVR topologies                                      | 86  |

|     | 5.2.2   | AC-AC converters-based DVR topologies                             | 87  |

| 5.3 | Matrix  | converter-based DVR: Input terminals connected on the supply side |     |

|     | (Topole | ogy I)                                                            | 90  |

|     | 5.3.1   | Modeling of the matrix converter DVR system                       | 90  |

|     | 5.3.2   | DVR controller                                                    | 95  |

| 5.4 | Matrix  | converter-based DVR: Input terminals connected on the load side   |     |

|     | (Config | guration 2)                                                       | 96  |

|     | 5.4.1   | Modeling of the matrix converter DVR system                       | 97  |

|     | 5.4.2   | DVR controller                                                    | 100 |

| 5.5 | Conclu  | sions                                                             | 101 |

| 5.6 | Referei | nces                                                              | 102 |

#### CHAPTER VI Simulation and Experimental Results

| 6.1 | Matrix | converter prototype                  | 105 |

|-----|--------|--------------------------------------|-----|

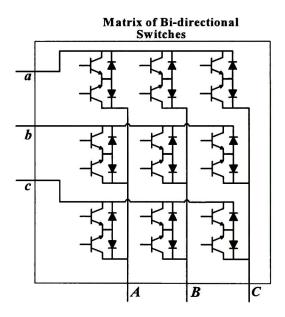

|     | 6.1.1  | Matrix of bidirectional switches     | 105 |

|     | 6.1.2  | The input filter                     | 108 |

|     | 6.1.3  | The control system                   | 111 |

| 6.2 | DVR t  | opology 1 Results                    | 113 |

|     | 6.2.1  | Numerical Verification               | 113 |

|     | 6.2.2  | Experimental Results                 | 119 |

| 6.3 | DVR t  | opology 2 Results                    | 123 |

|     | 6.3.1  | Numerical Verification               | 123 |

|     | 6.3.2  | Experimental Results                 | 127 |

| 6.4 | Concl  | usions                               | 128 |

| 6.5 | Refere | ences                                | 128 |

|     |        |                                      |     |

| CH  | APTER  | R VII Conclusions and Future Work    |     |

|     |        |                                      |     |

| 7.1 | Concl  | usions                               | 129 |

| 7.2 |        | butions                              | 130 |

| 7.3 | Recon  | nmendations for future work          | 131 |

| 7.4 | Activi | ties developed during the Ph. D.     | 132 |

| 7.5 | List o | f publications                       | 132 |

|     |        |                                      |     |

| API | PENDI  | X A Commutation Vectors              |     |

| A.1 | Input- | voltage vectors in the complex space | 133 |

| A.2 |        | hing states                          | 134 |

|     | A.2.1  | Switching states analysis            | 135 |

# List of Figures

|           |                                                                                                           | _  |

|-----------|-----------------------------------------------------------------------------------------------------------|----|

| Fig. 2.1  | Sources of power quality problems                                                                         | 8  |

| Fig. 2.2  | Voltage disturbances                                                                                      | 9  |

| Fig. 2.3  | Voltage harmonics propagation                                                                             | 11 |

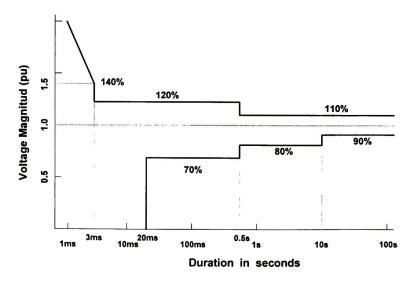

| Fig. 2.4  | ITIC curve                                                                                                | 12 |

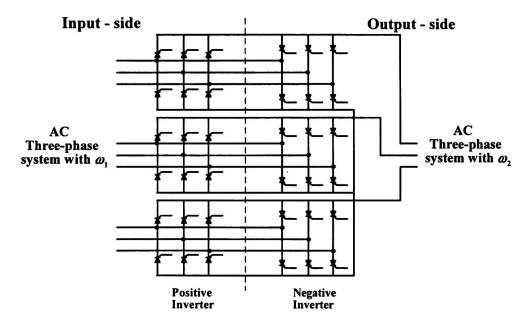

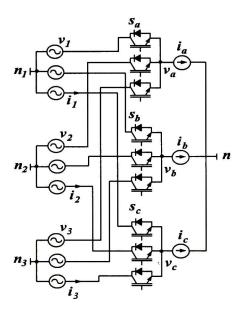

| Fig. 2.5  | Three phase-to-three phase NCC                                                                            | 17 |

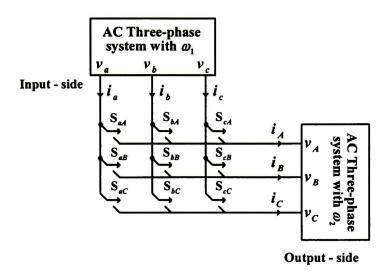

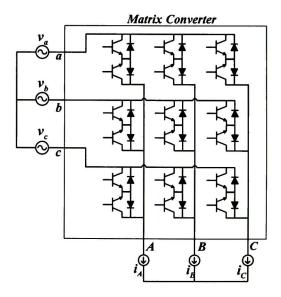

| Fig. 2.6  | Three phase-to-three phase matrix converter                                                               | 19 |

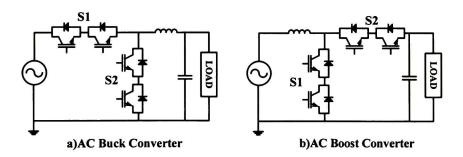

| Fig. 2.7  | AC-AC voltage regulator topologies                                                                        | 19 |

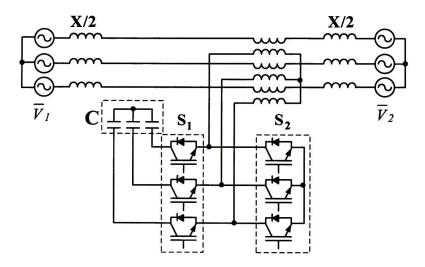

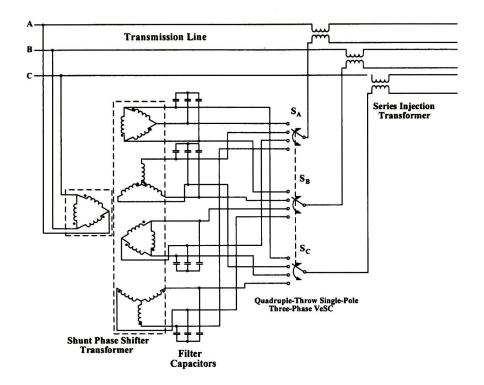

| Fig. 2.8  | AC-link converter-based series compensator (Xi controller)                                                | 20 |

| Fig. 2.9  | Gamma controller                                                                                          | 21 |

| Fig. 2.10 | 3X1 Vector switching converter                                                                            | 21 |

| Fig. 3.1  | Basic matrix converter structure                                                                          | 30 |

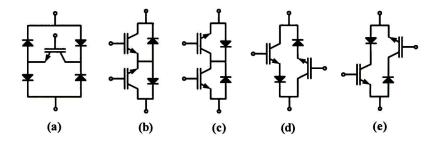

| Fig. 3.2  | Bidirectional switch topologies using unidirectional components                                           | 32 |

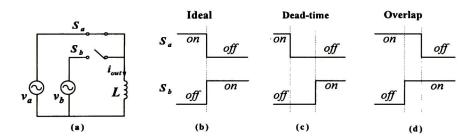

| Fig. 3.3  | Commutation of the out phase from the input phase: a) Power circuit;                                      | 22 |

|           | b) Ideal commutation; c) Dead-time commutation; d) Overlap commutation                                    | 33 |

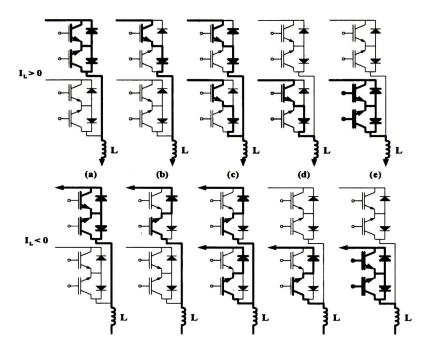

| Fig. 3.4  | Path current allowed during four-step commutation                                                         | 35 |

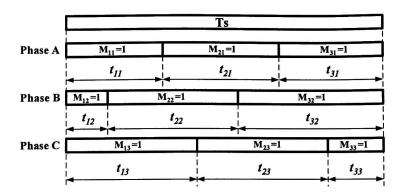

| Fig. 3.5  | Typical switching pattern                                                                                 | 36 |

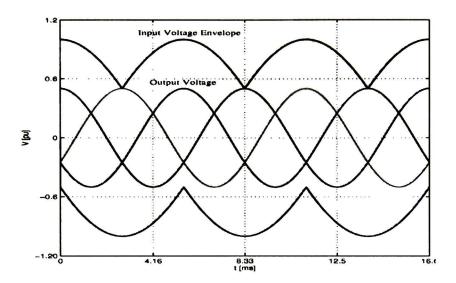

| Fig. 3.6  | Output voltage limited to 50%                                                                             | 39 |

| Fig. 3.7  | Maximum output voltage (86.6%)                                                                            | 40 |

| Fig. 3.8  | Reference vector tracking                                                                                 | 42 |

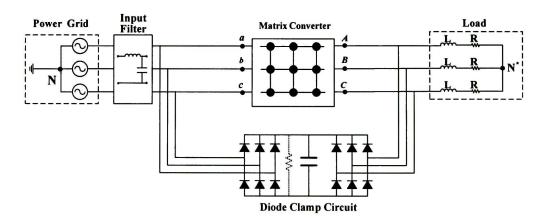

| Fig. 3.9  | Diode clamp in matrix converter applications                                                              | 44 |

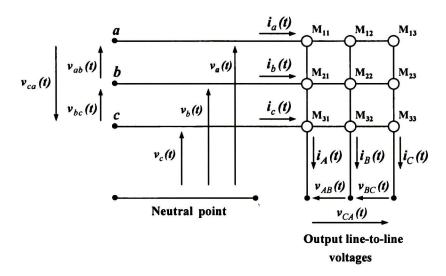

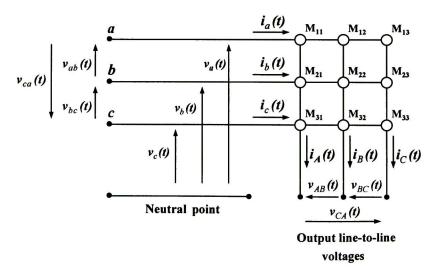

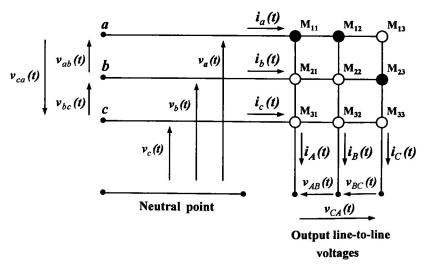

| Fig. 4.1  | Conversion matrix basic structure                                                                         | 51 |

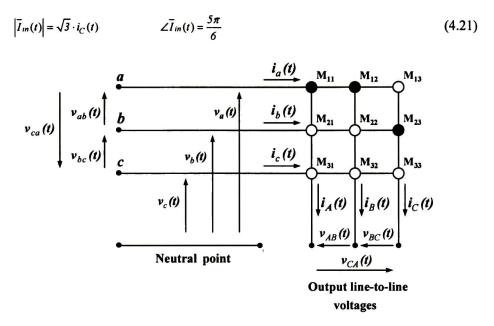

| Fig. 4.2  | Matrix topology for state S2                                                                              | 57 |

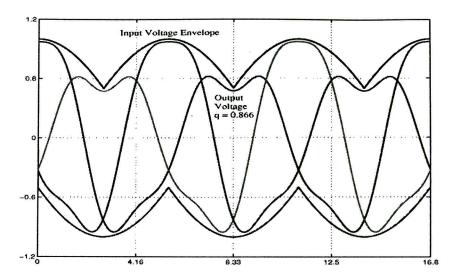

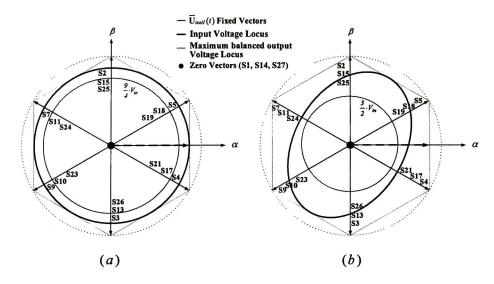

| Fig. 4.3  | a) Voltage vectors for balanced input voltage condition. b) voltage vectors                               | 50 |

|           | for unbalanced conditions (sag of 50% on phase $b$ ).                                                     | 58 |

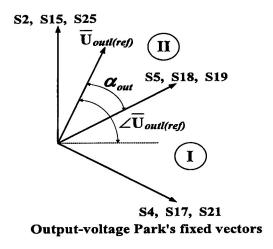

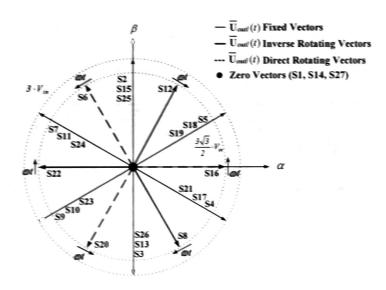

| Fig. 4.4  | Output-voltage's fixed vectors                                                                            | 58 |

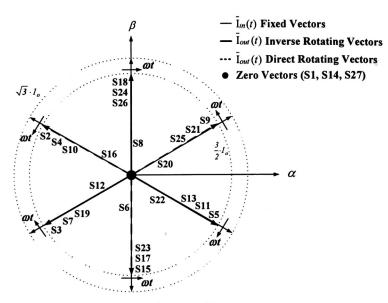

| Fig. 4.5  | Input current's fixed vectors                                                                             | 58 |

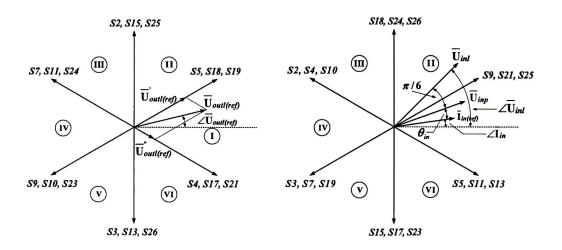

| Fig. 4.6  | $\overline{U}_{out(ref)}$ tracking                                                                        | 59 |

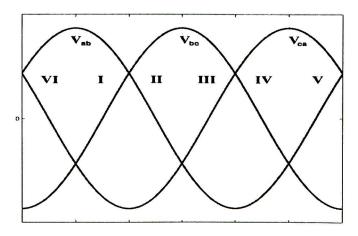

| Fig. 4.7  | Relationship between line-to-line input voltages and $\overline{U}_{np}$ vector's sectors                 | 60 |

| Fig. 4.8  | Required states for tracking $\overline{U}_{outl(ref)}$ when $\overline{U}_{inp}$ is in sector I          | 61 |

| Fig. 4.9  | $\overline{I}_{m(ref)}$ tracking                                                                          | 62 |

| Fig. 4.10 | $\alpha_{out}$ definition                                                                                 | 68 |

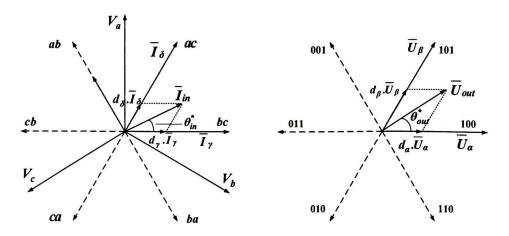

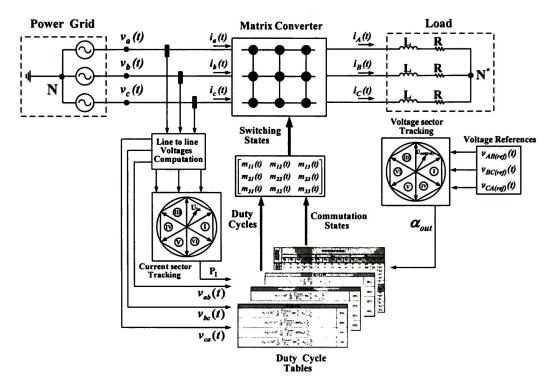

| Fig. 4.11 | System architecture to simulate the modified DSVM control algorithm                                       | 69 |

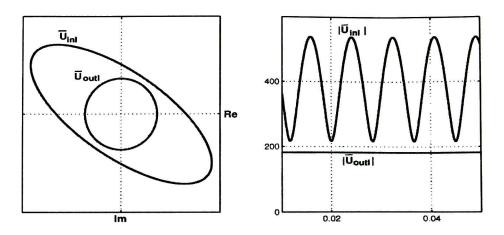

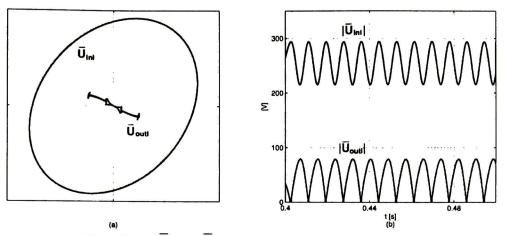

| Fig. 4.12 | From left to right: $\overline{U}_{inl}$ and $\overline{U}_{outl(ref)}$ Park vectors in the complex space |    |

|           | Vectors magnitude                                                                                         | 70 |

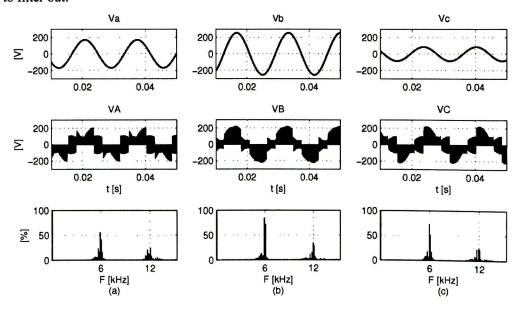

| Fig. 4.13 | From Top to bottom: Input phase voltages, Output phase voltages and                                       |    |

| 0         | output voltage harmonic spectrum (as percent of the fundamental                                           |    |

|           | component). a)Phase $a$ , b) Phase $b$ , c) Phase $c$                                                     | 70 |

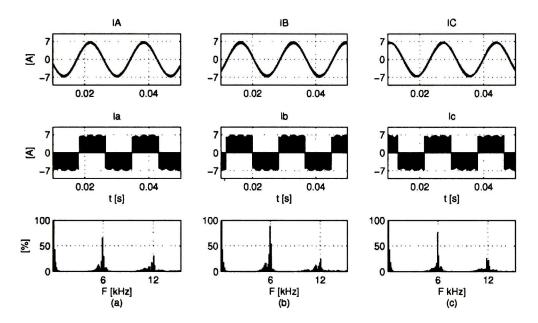

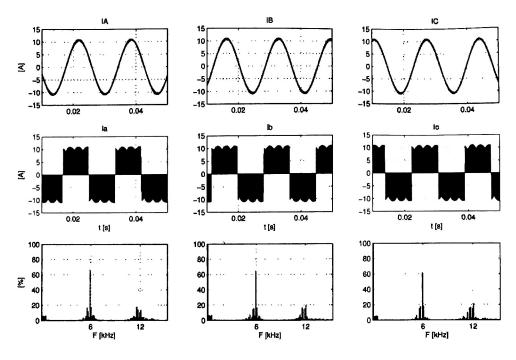

| Fig. 4.14 | From Top to bottom: Output currents, Input currents and Input currents                               |    |

|-----------|------------------------------------------------------------------------------------------------------|----|

|           | harmonic spectrum (as percent of the fundamental component)                                          | 71 |

| E:- 4 16  | a) Phase a, b) Phase b, c) Phase c.                                                                  | 71 |

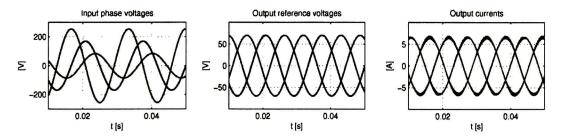

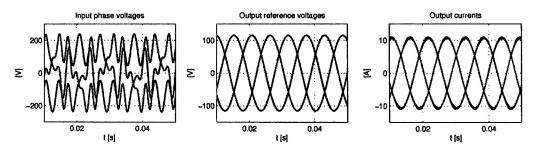

| Fig. 4.15 | From left to right: Input phase voltages, Output voltage references                                  | 71 |

|           | and Output currents                                                                                  | 71 |

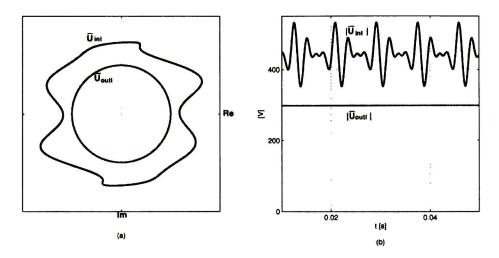

| Fig. 4.16 | a) $\overline{U}_{inl}$ and $\overline{U}_{outl(ref)}$ Park vectors in the complex space. b) Vectors |    |

|           | Magnitude                                                                                            | 73 |

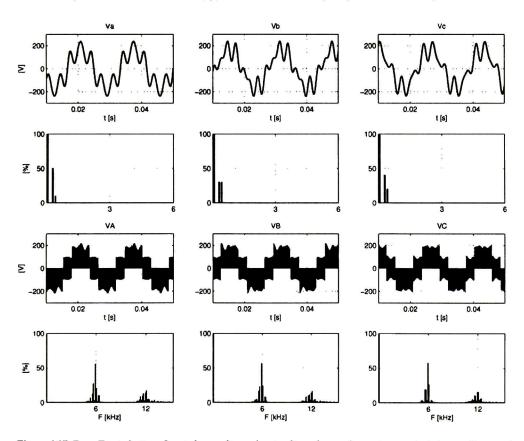

| Fig. 4.17 | From Top to bottom: Input phase voltages, input voltages harmonic                                    |    |

|           | spectrum, output phase voltages and output voltage harmonic spectrum                                 |    |

|           | (Harmonics expressed as percent of the fundamental component)                                        | 73 |

| Fig. 4.18 | From Top to bottom: Output currents, Input currents and Input currents                               |    |

|           | harmonic spectrum (as percent of the fundamental component)                                          | 74 |

| Fig. 4.19 | From left to right: Input phase voltages, Output voltage references and                              |    |

|           | Output currents                                                                                      | 74 |

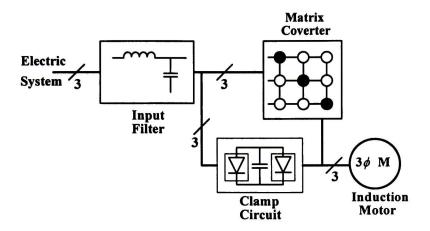

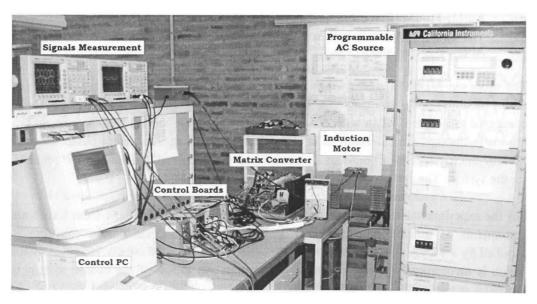

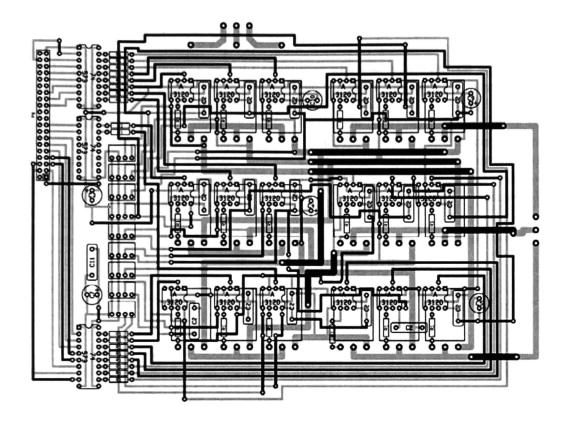

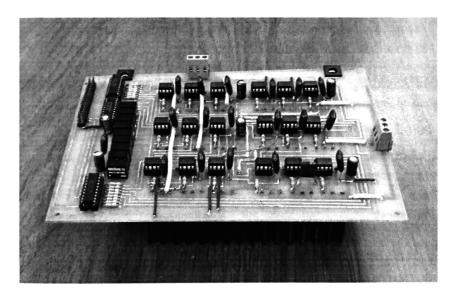

| Fig. 4.20 | Schematic diagram of the matrix converter prototype                                                  | 75 |

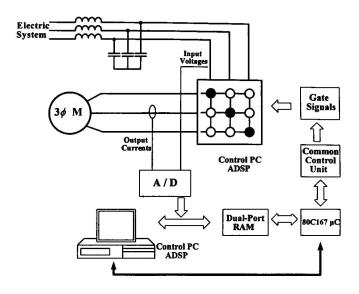

| Fig. 4.21 | Schematic diagram of the matrix converter control system                                             | 76 |

| Fig. 4.22 | Image of the matrix converter prototype (Laboratory of the Institute of                              |    |

|           | Energy Technology, Aalborg University, Denmark)                                                      | 76 |

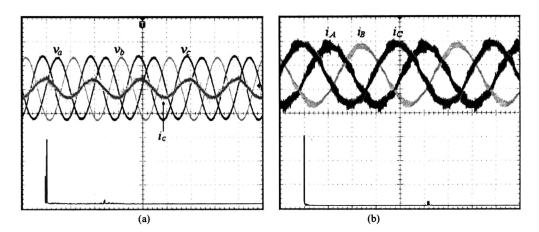

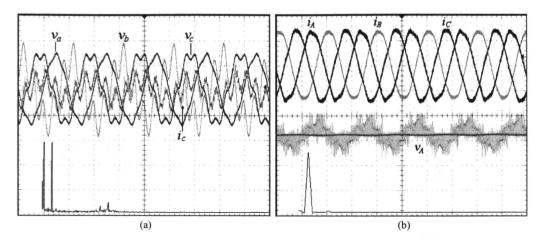

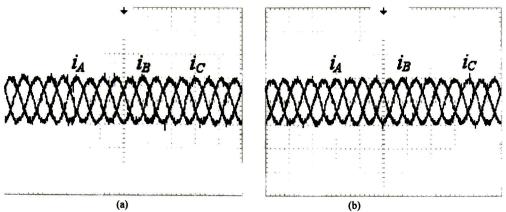

| Fig. 4.23 | a) Input voltages (100V/div, 10ms/div), Phase c Input current                                        |    |

|           | (2A/div, 10ms/div) and input current FFT (200mA/div, 625 Hz/div).                                    |    |

|           | b) Output currents (1A/div, 10ms/div) and phase a output current FFT                                 |    |

|           | (250mA/div, 1.25 kHz/div)                                                                            | 77 |

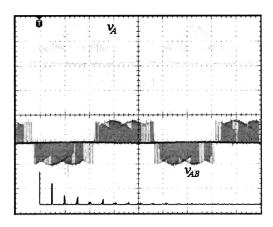

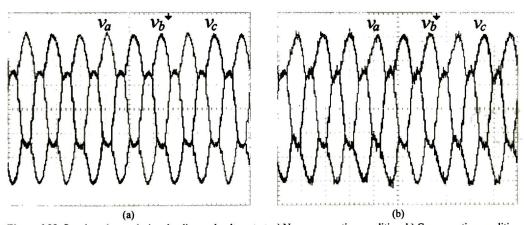

| Fig.4.24  | Phase a output voltage (50V/div, 4ms/div), Line-to-line output voltage                               |    |

|           | (250V/div, 4ms/div). Bottom: Phase voltage FFT (50V/div, 12.5 kHz/div)                               | 77 |

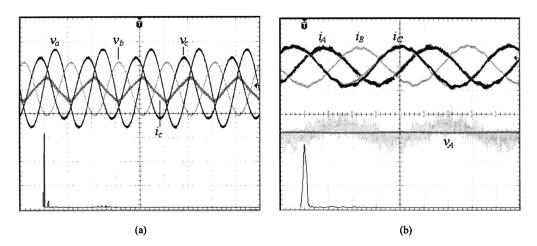

| Fig. 4.25 | a) Input voltages (100V/div,10ms/div),Phase c input current                                          |    |

|           | (2A/div, 10ms/div) and input current FFT (200mA/div, 625 Hz/div)                                     |    |

|           | b) Output currents (1A/div, 10ms/div), Phase a output voltage                                        |    |

|           | (50V/div, 10ms/div). Bottom: Phase a output current FFT                                              |    |

|           | (200mA/div, 125 Hz/div)                                                                              | 78 |

| Fig.4.26  | a) Input voltages (100V/div,10ms/div), Phase c input current                                         |    |

|           | (2A/div,10ms/div) and input current FFT (200mA/div,625 Hz/div)                                       |    |

|           | b) Output currents (1A/div, 10ms/div), Phase a output voltage                                        |    |

|           | (50V/div, 10ms/div). Bottom: Phase a output current FFT                                              |    |

|           | (400mA/div,125 Hz/div)                                                                               | 79 |

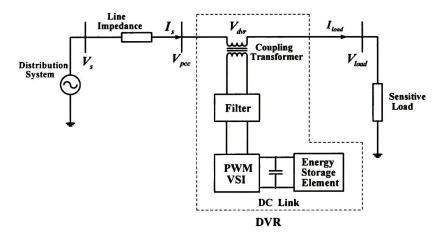

| Fig. 5.1  | Typical schematic of a power distribution system compensated by a DVR                                | 84 |

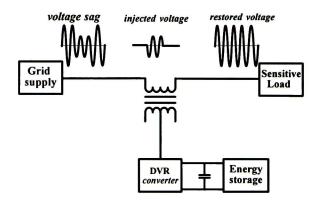

| Fig. 5.2  | Operational principle of a dynamic voltage restorer (DVR)                                            | 84 |

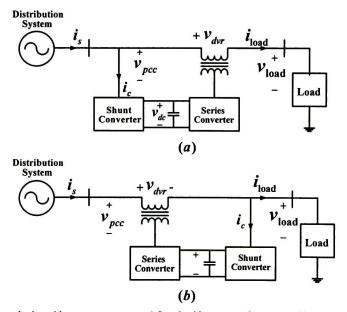

| Fig. 5.3  | DVR topologies with no energy storage. a) Supply side connected                                      |    |

|           | Converter. b) Load side connected shunt converter                                                    | 86 |

| Fig.5.4   | DVR topologies with energy storage. a) Variable DC-link voltage. b) With                             |    |

|           | Constant DC-link voltage                                                                             | 87 |

| Fig. 5.5  | AC-AC DVR without energy storage devices                                                             | 88 |

| Fig. 5.6  | AC-AC DVR with energy storage device                                                                 | 89 |

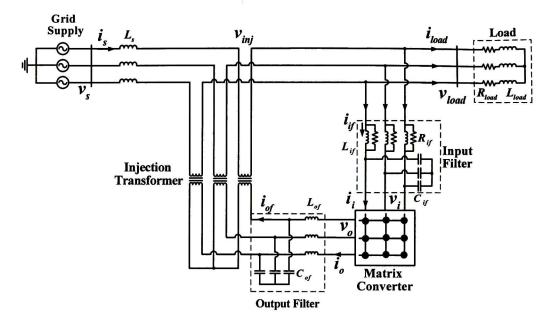

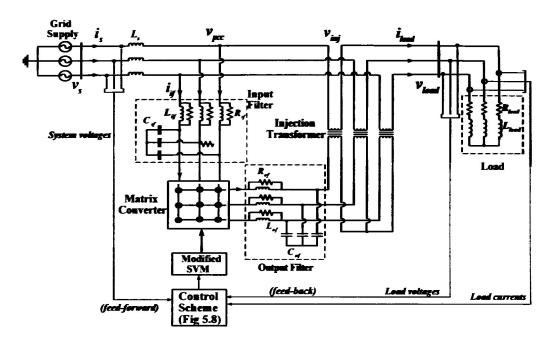

| Fig. 5.7  | Proposed DVR with matrix converter input terminals connected on the                                  |    |

|           | supply side                                                                                          | 91 |

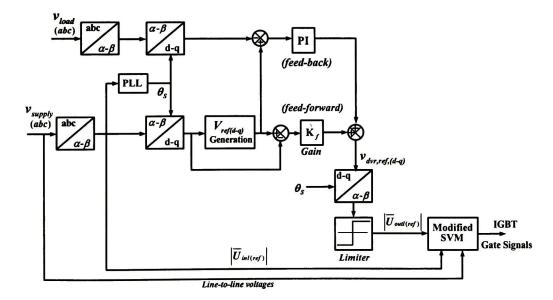

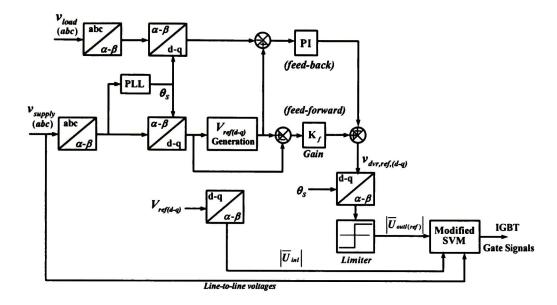

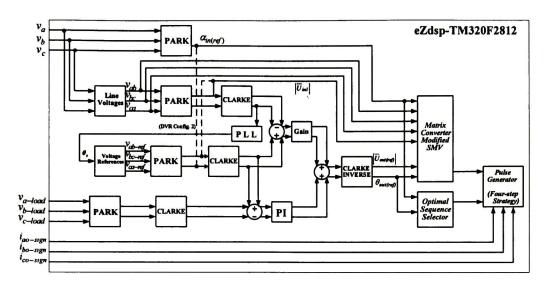

| Fig. 5.8  | Proposed DVR control scheme                                                                              | 95  |

|-----------|----------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.9  | Proposed DVR with matrix converter input terminals connected on the load                                 |     |

|           | side                                                                                                     | 97  |

| Fig. 5.10 | Proposed DVR configuration 2 control scheme                                                              | 101 |

| Fig. 6.1  | Matrix converter structure with IGBT's in common-emitter configuration                                   | 106 |

| Fig. 6.2  | Matrix converter PCB layout                                                                              | 107 |

| Fig. 6.3  | Matrix converter prototype                                                                               | 107 |

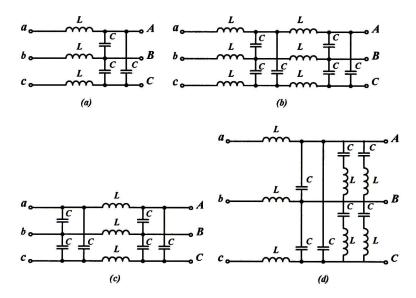

| Fig. 6.4  | LC Filter configurations. a) One-stage LC filter, b) Multi-stage LC filter,                              |     |

|           | c) $\pi$ LC filter, and d) One-stage LC filter with notch addition                                       | 108 |

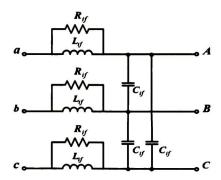

| Fig. 6.5  | LC Filter with the addition of a damping resistor                                                        | 109 |

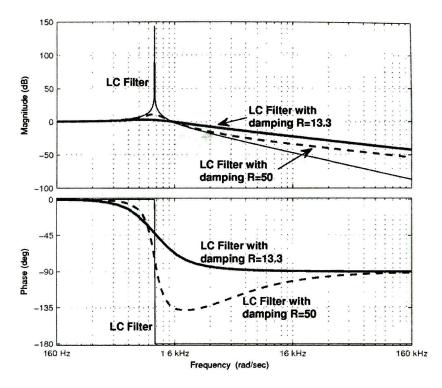

| Fig. 6.6  | Frequency response for L-C filter with and without damping resistor                                      |     |

|           | (L=2.2 mH, C= $10\mu F$ , R = $13.3 \Omega$ , R= $50 \Omega$ ). Top: Magnitude response                  |     |

|           | Bottom: Phase response                                                                                   | 110 |

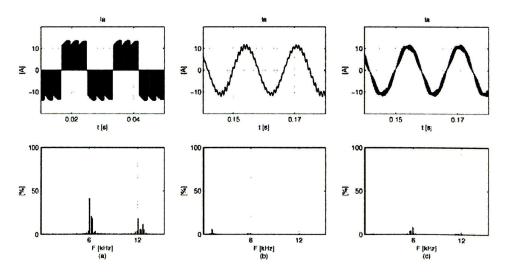

| Fig. 6.7  | Harmonic analysis of phase $a$ input current made with PSCAD software.                                   |     |

|           | a) Without filter, b) With One-stage LC filter, c) With One-stage LC filter                              |     |

|           | with damping resistor (R = $13.3 \Omega$ )                                                               | 110 |

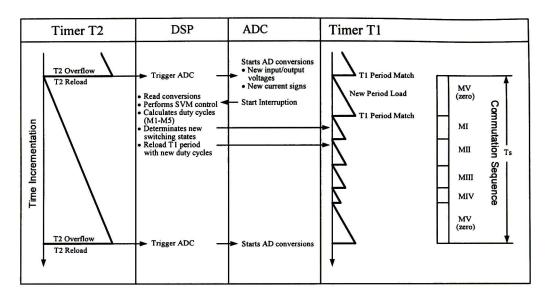

| Fig. 6.8  | Control system task management of the matrix converter prototype                                         | 112 |

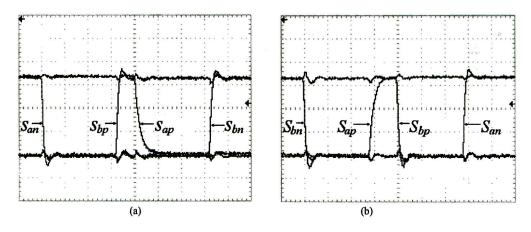

| Fig. 6.9  | Signals generated by the DSP on the four step commutation strategy. (a)                                  |     |

|           | Commutation from phase $a$ to phase $b$ . b) Commutation from phase $b$ to                               |     |

|           | phase a. (1V/div, 100ns/div)                                                                             | 112 |

| Fig. 6.10 | DSP control for the matrix converter prototype                                                           | 113 |

| Fig. 6.11 | Proposed DVR topology 1 system architecture                                                              | 114 |

| Fig. 6.12 | a) Vectors $\overline{U}_{inl}$ and $\overline{U}_{out(ref)}$ in the complex space. b) Vectors magnitude | 115 |

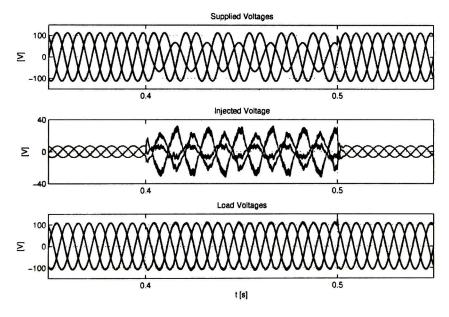

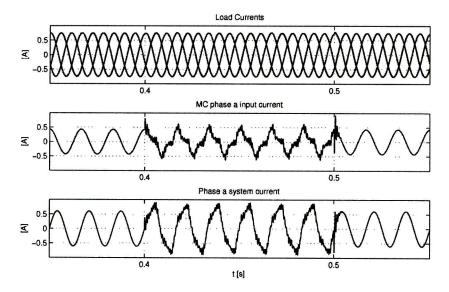

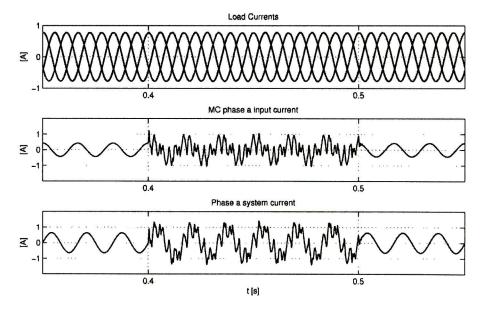

| Fig. 6.13 | DVR response under unbalanced voltage variation. From top to bottom:                                     |     |

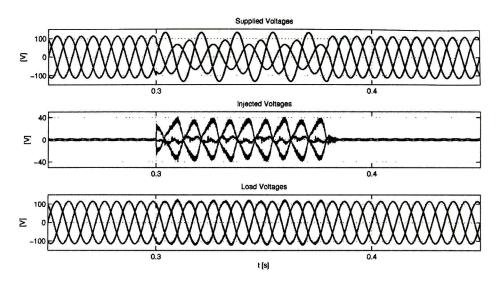

|           | Supply voltages, injected voltages and load voltages                                                     | 115 |

| Fig. 6.14 | DVR response under unbalanced voltage variation. From top to bottom:                                     |     |

|           | Load currents, matrix converter phase a input current and supply system                                  |     |

|           | current phase a                                                                                          | 116 |

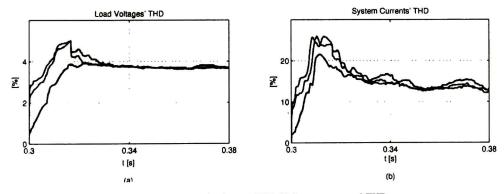

| Fig. 6.15 | a) Load voltages' THD. b) System supply currents' THD                                                    | 116 |

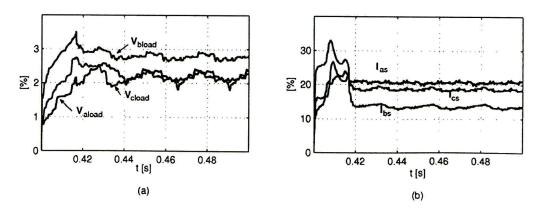

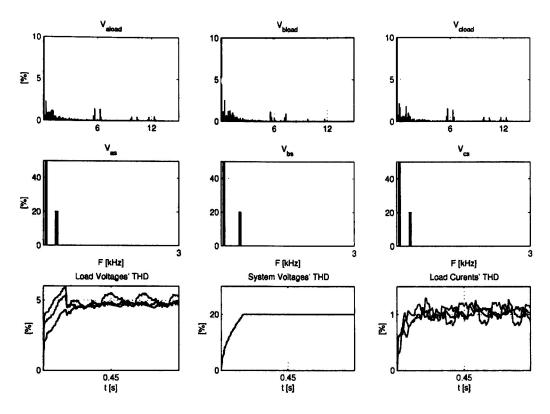

| Fig. 6.16 | a) $\overline{U}_{inl}$ and $\overline{U}_{outl}$ in the complex space. b) Vectors magnitude             | 117 |

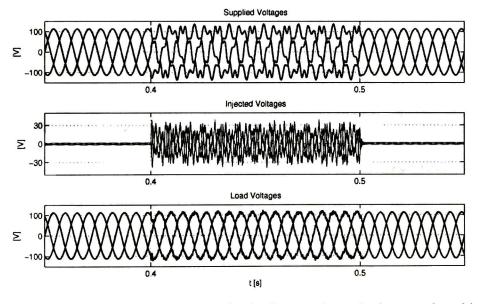

| Fig. 6.17 | DVR response under voltage with harmonic distortion. From top to bottom:                                 |     |

|           | Supply system voltages, injected voltages and load voltages                                              | 117 |

| Fig. 6.18 | DVR response under voltage with harmonic distortion. From top to bottom:                                 |     |

|           | Load currents, matrix converter phase a input current and supply system                                  |     |

|           | phase a current                                                                                          | 118 |

| Fig. 6.19 | From top to bottom: Harmonic content of load voltages, harmonic content                                  |     |

|           | of system voltages and main signals' THD                                                                 | 119 |

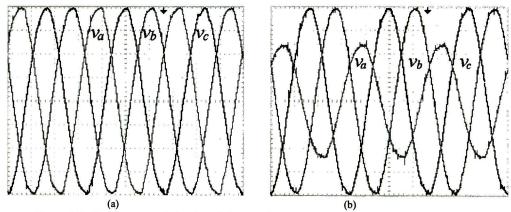

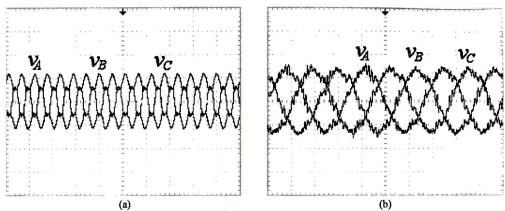

| Fig. 6.20 | Supply voltages during the unbalanced voltage sag test. a) Pre-sag condition.                            |     |

|           | b) Sag condition. (20V/div,5ms/div)                                                                      | 120 |

| Fig. 6.21 | Load voltages during the unbalanced voltage sag test. a) Pre-sag condition                               |     |

|           | b) Sag condition. (50V/div, 10ms/div)                                                                    | 120 |

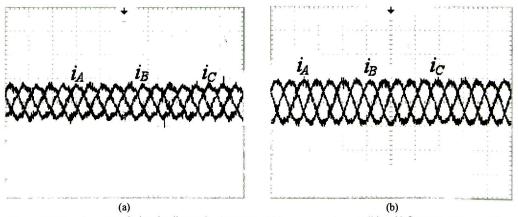

| Fig. 6.22 | Load currents during the unbalanced voltage sag test. a) Pre-sag condition                               |     |

|           | b) Sag condition. (0.5A/div,10ms/div)                                                                    | 121 |

| Fig. 6.23 | Supply voltages during the distorted voltage test. a) No-compensation                                    |     |

|           | condition. b) Compensation condition. (20V/div, 5ms/div)                        | 121 |

|-----------|---------------------------------------------------------------------------------|-----|

| Fig. 6.24 | Load voltages during the distorted voltage test. a) No-compensation             |     |

|           | condition (50V/div, 10ms/div). b) Compensation condition                        |     |

|           | (50V/div, 5ms/div)                                                              | 122 |

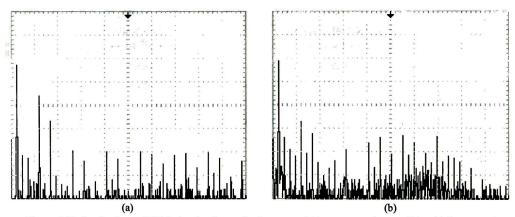

| Fig. 6.25 | Load voltages FFT during the distorted voltage test. a) No-compensation         |     |

|           | condition. b) Compensation condition. (10dB/div, 250Hz/div)                     | 122 |

| Fig. 6.26 | Load currents during the distorted voltage test. a) No-compensation             |     |

|           | condition. b) Compensation condition. (0.5A/div, 10ms/div)                      | 122 |

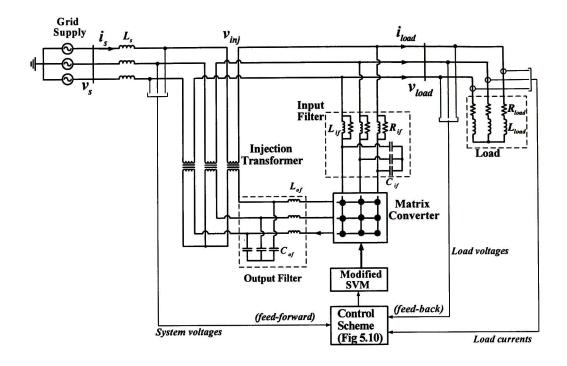

| Fig. 6.27 | Proposed DVR topology 2 system architecture                                     | 124 |

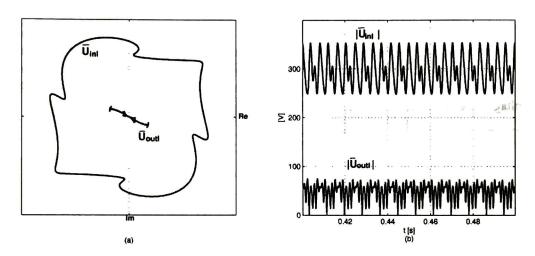

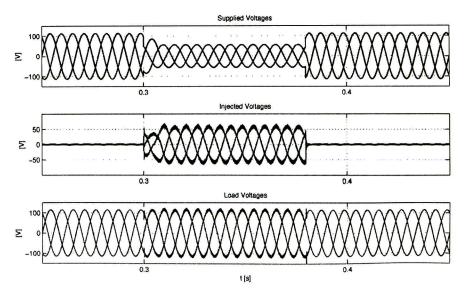

| Fig. 6.28 | DVR response for balanced voltage sag compensation. From top to bottom:         |     |

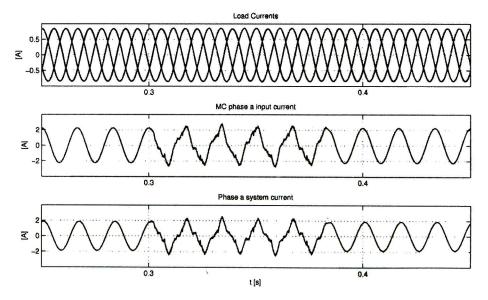

|           | Supply voltages, Injected voltages and Load voltages                            | 124 |

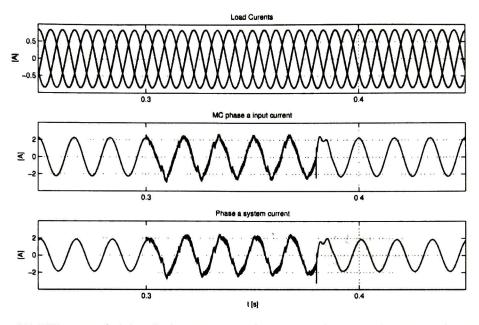

| Fig. 6.29 | DVR response for balanced voltage sag compensation. From top to bottom:         |     |

|           | Load currents, matrix converter phase a input current and Phase a supply        |     |

|           | system current                                                                  | 125 |

| Fig. 6.30 | a) Load voltages' THD. b) System currents' THD                                  | 125 |

| Fig. 6.31 | DVR response for unbalanced voltage disturbance. From top to bottom:            |     |

|           | Supply voltages, Injected voltages and Load voltages                            | 120 |

| Fig. 6.32 | DVR response for unbalanced voltage disturbance. From top to bottom:            |     |

|           | Load currents, matrix converter phase a input current and Phase a supply        |     |

|           | system current                                                                  | 126 |

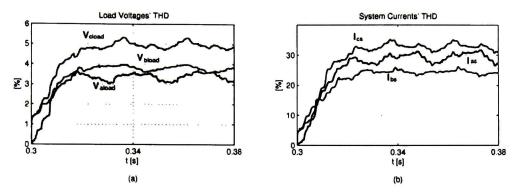

| Fig. 6.33 | a) Load Voltages' THD. b) System currents' THD                                  | 127 |

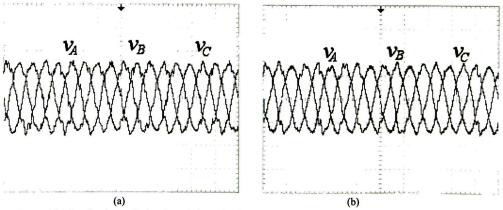

| Fig. 6.34 | a) Pre-sag condition. b) Sag condition. Ch 1: Load current (0.5 A/div),         |     |

|           | Ch 2: Load voltage (20V/div), Ch 3: Supply voltage (20V/div, 5ms/div)           | 127 |

| Fig. 6.35 | a) Pre-sag condition (0.5 A/div, 5ms/div). b)Sag condition. Load currents       |     |

|           | (0.5 A/div, 10ms/div)                                                           | 128 |

| Fig. A.1  | Conversion matrix basic structure                                               | 134 |

| Fig. A.2  | Conversion matrix topology for state 2                                          | 130 |

| Fig. A.3  | Vectors $\overline{U}_{out}(t)$ in the complex space                            | 13′ |

| Fig. A.4  | Vectors $\overline{I}_{in}(t)$ and $\overline{I}_{out}(t)$ in the complex space | 13  |

# List of Tables

| Table 2.1 | Effect of voltage imbalance on motors at rated load                 | 11  |

|-----------|---------------------------------------------------------------------|-----|

| Table 2.2 | Voltage distortion guidelines for power systems                     | 13  |

| Table 4.1 | DSVM vector sequences                                               | 66  |

| Table 4.2 | Duty cycles for $P_I = I$ and $IV$                                  | 66  |

| Table 4.3 | Duty cycles for $P_I = II$ and $V$                                  | 67  |

| Table 4.4 | Duty cycles for $P_I = III$ and $VI$                                | 67  |

| Table 4.5 | List of parameters                                                  | 68  |

| Table 6.1 | System Parameters                                                   | 114 |

| Table 6.2 | System Parameters                                                   | 119 |

| Table 6.3 | System 2 parameters                                                 | 123 |

| Table A.1 | Permitted switching states in a three phase to three phase matrix   |     |

|           | Converter                                                           | 136 |

| Table A.2 | Park's vector arguments and modulus line-to-line output voltage and |     |

|           | Input current for each commutation state (Zero Vectors)             | 138 |

| Table A.3 | Park's vector arguments and modulus line-to-line output voltage and |     |

|           | Input current for each commutation state (Rotating Vectors)         | 138 |

| Table A.4 | Park's vector arguments and modulus line-to-line output voltage and |     |

|           | Input current for each commutation state (Fixed Vectors)            | 139 |

|           |                                                                     |     |

# List of Acronyms

EPS Electric Power System

CUPS Custom Power System

DVR Dynamic Voltage Restorer

SMES Super Magnetic Energy Storage

MDSVM Modified Direct Space Vector Modulation

IGBT Insulated Gate Bipolar Transistor

DSP Digital Signal Processor

CEA Canadian Electric Association

EPRI Electric Power Research Institute

NPL National Power Laboratory

PCC Point of Common Coupling

ANSI American National Institute

IEEE Institute of Electrical and Electronics Engineers

ITIC Information Technology Industry Council

CENELEC European Committee for Electrotechnical Standarization

IEC International Electrotechnical Commission

IEEE-IAS Institute of Electrical and Electronics Engineering, Industry

**Application Society**

NEMA National Electric Manufactures Association

FACTS Flexible Alternating Current Transmission Systems

SSSC Static Synchronous Series Compensator

TSSC Thyristor Switched Series Capacitor

TSSR Thyristor Switched Series Reactor

SSG Static Synchronous Generator

SVG Static Var Generator STATCOM Static compensator

TCR Thyristor Controlled Reactor

TSC Thyristor Switched Capacitor

UPFC Unified Power Flow Controller

DSTATCOM Distribution Static Compensator

UPQC Unified Power Quality Conditioner

NCC Naturally Commutated Cycloconverter

VeSC Vector Switching Converter

SCR Silicon Controlled Rectifier

THD Total Harmonic Distortion

FRD Fast Recovery Diode

CSC Current Switch Clamped

VSI Voltage Source Inverter

PWM Pulse Width Modulation

SVM Space Vector Modulation

ISVM Indirect Space Vector Modulation

DSVM Direct Space Vector Modulation

ADC Analog / Digital Converter

### CHAPTER I

### Introduction

#### 1.1 Introduction and Motivation

Nowadays, electricity supply industry has been experienced extraordinary changes mainly aroused by the imminent scarcer of natural resources, the continuously energy demand increments and the quality of delivered energy concerned. All these reasons, together with a variety of environmental and regulatory pressures that prevent the building of new power generating plants and transmission lines, are taking the power systems to operate close to their stability and thermal limits.

Among the actual issues related to electric power systems (EPS's), the term electric power quality has gained considerable attention by both electric suppliers and end users. From the standpoint of utilities, the major concern relies on fact that contemporary devices and equipment (electronic-based systems) being used by industrial and commercial customers are more sensitive to power quality variations than equipment used in the past. From the power grid point of view, the increment of electronic loads becomes important sources of power quality degradation, which causes a growth in the application of passive devices as capacitors for harmonic filtering and power factor correction. These capacitors change the system impedance resulting in possible resonance, which can magnify transient disturbances and harmonic distortion levels.

Power quality delivery refers to the ability of transmission and distribution systems to deliver the electric power to any point of consumption in the amount and quality demanded by the customer. Every system has different influence on the level of the quality of delivery. For example, a failure in a transmission component may lead to subsequent loss in distribution power. A failure in distribution components only causes local losses in costumer loads. Whereas problems related to power transmission systems and power distribution systems are all fundamental from power quality point of view, only some distribution systems issues are considered in this dissertation.

Deterioration of energy at distribution levels can be caused by natural causes: faults or lightning strikes in feeders and equipment failure, by feeder line operation or loads. For instance, power electronic based loads, switching on/off large loads etc. When one of this events occurs somewhere in a distribution system, the voltage is affected throughout it. Therefore the term power quality includes two important aspects [1.1]:

- Voltage quality. Involves rapid changes, harmonics, interharmonics, imbalance, etc.

- Supply Reliability. Involves phenomena with longer duration, voltage sags, swells, interruptions, etc.

As stated above, in front of the importance acquired by power quality topics in EPS's there is a general agreement by researchers worldwide, that novel power electronics equipment is a potential substitute for conventional solutions, which are normally based on electromechanical technologies that have slow response and high maintenance costs [1.2]. As conventional devices are being inefficient for actual power delivery problems, many researchers have focused their efforts in the developing of novel control strategies and operational techniques in order to replace them [1.3]. In the present investigation two novel topologies are proposed for a Custom Power System (CUPS) device, with the purpose of mitigate some of the common power quality problems found on electric distribution systems.

#### 1.2 Justification

As mentioned above, the actual technological advance achieved in the power electronics area has allowed the optimization of a diversity of components inside the EPSs, particularly in the energy conditioning field. On the other hand, this tendency has given rise to the appearance of new issues in power transmission and distribution systems, which implies a huge challenge. One of the main concerns in which researches around the world have been focused on, is the power quality topic. The adverse effects caused by sags or swells in the manufacture process and sensitive loads have been described in several publications [1.4]-[1.7]. Likewise, the voltage harmonics problematic has been broached in manifold publications [1.8]-[1.10]. In general, power quality issues become direct factors of economic losses. Hence, the development of Custom Power Systems for improving the power system operation is imperative.

The series compensation device DVR (Dynamic Voltage Restorer) was introduced for voltage sag mitigation and has been adopted as a common solution to the problem. Since its introduction in 1994, several topologies have been developed, along with different control

methods and with harmonic compensation purposes [1.11]-[1.14]. While DVR topologies with energy storage are highly favored to compensate deep level voltage sags, this type of systems has significant drawback regarding complexity and overall cost.

Most of the DVR topologies presented in the literature share one specific characteristic: the DC-link. In order to eliminate the drawbacks imposed by the use of DC-link passive elements, some researchers have focused their efforts in develop novel topologies based on AC-AC power conversion [1.6], [1.15]-[1.8]. The advantages of utilizing AC-AC converters as an alternative to the use of DC-link converters are listed:

- The presence of huge electrolytic capacitors or another external storage system as batteries, super-capacitors or super magnetic energy storage (SMES) is not required.

- Reduced maintenance requirements

- · High Power density

- Reduced harmonic level of low frequencies in the input current

Among the AC-link conversion topologies aimed to operate as a voltage compensator, the matrix converter offers the next operative advantages:

- Theoretically a non limited output frequency

- High quality output voltage and input current waveforms

- Controllable input power factor

- Four quadrant operation

- Excellent dynamic response

- Compact design

A further analysis of matrix converter is presented along with novel DVR topologies based on this device.

#### 1.3 Objectives and Contributions

This dissertation proposes a Modified Direct Space Vector Modulation (MDSVM) strategy to control the matrix converter voltage generation which is developed from the analysis of voltage and current Park vectors in the complex space, considering a set of three phase unbalanced input voltages. The precise control of the reference vectors allows generating a set of controllable voltages in magnitude, phase and frequency. Control of the phase voltages are accomplished independently, characteristic that allows the matrix converter to operate as a voltage compensator which results in the proposition of two novel DVR topologies based on the AC-AC converter.

Through the proposed DVR topologies, this dissertation addresses the more common power quality problems, in particular sags, swells, unbalanced and harmonic voltages. Together, they account for more than 90% of the power quality disturbances affecting most commercial and industrial customers. Simulation and experimental results are provided to verify the proposed configurations. The hardware implementation of the matrix converter is based on IGBTs and DSP control.

Taking into account the operative features achieved through the combination of the feed-back-feed-forward controller and the MDSVM strategy, the proposed DVR topologies become an economical effective solution to overcome the power quality problems in electric distribution systems.

The main contributions of current research work are summarized as follows:

- The mathematical development of the MDSVM to control the matrix converter operation

- Design of two novel multi-functional DVR topologies based on the matrix converter

- Numerical evaluation of the proposed DVR topologies dynamic performance through a detailed model implemented in PSCAD software

- Implementation of a laboratory-scale prototype of the matrix converter based DVR

#### 1.4 Thesis Outline

The thesis organization is as follows:

Chapter II. A brief overview of the power quality issues including literature surveys about voltage disturbances, related industrial standards, and mitigation schemes are presented. This chapter is focused on the more common power quality problems: sags, swells, unbalanced and harmonic distortion in voltages.

Chapter III. This chapter presents the matrix converter state-of-the-art. A historical review is carried out based on the literature, towards matrix converter introduction. Then, theoretical and practical basic concepts are reviewed to completely understand the AC-AC converters operational principle, emphasizing advantages and drawbacks of this technology, towards matrix converter practical implementation. Finally, commutation techniques and modulation strategies are analyzed and compared.

Chapter IV. In this chapter the proposed MDSVM strategy is developed which is one of the main objectives of this dissertation. The MDSVM technique is based on the direct DSVM modulation in which the output voltage and input current are controlled by means of magnitude and phase modification of the reference vectors in the complex space. Simulation and experimental results over various adverse conditions are presented to verify the strategy's effectiveness.

Chapter V. In chapter V, this research proposes two DVR's topologies for voltage compensation incorporating the matrix converter technology. The DVR's operational principle is presented, along with a comparison of the conventional topologies. After analyzing different schemes, and according to the objectives above mentioned, the final topologies are justified and the basic configurations are presented. To efficiently mitigate the voltage disturbance, a voltage controller is designed and explained. Finally the state-space equations for both system configurations are derived.

Chapter VI. Simulation results of voltage disturbances are presented to show the fast control response and the well-regulated output voltage using the proposed scheme. Experiments have been carried out to demonstrate the validity of the proposed topologies and results are presented in this chapter. Likewise, the hardware configuration is briefly explained.

Chapter VII. The conclusions and contributions resulting from this research work are presented in this chapter. Recommendations for future research on this topic are also provided.

#### 1.5 References

- [1.1] CIGRE Working group: "Custom Power state of the art", 1999.

- [1.2] N. G. Hingorani and L. Gyugyi, "Understanding FACTS: Concepts and technology of flexible AC transmission," *IEEE*, New York 2000.

- [1.3] G. Reed, M. Takeda, I. Iyoda, "Improved power quality solutions using advanced solid-state switching and static compensation technologies," in *Proceedings of IEEE PES'99 Winter Meeting*, pp. 1132-1137, February 1999.

- [1.4] Su Chen: "DSP-Based control of static power quality compensators in industrial power systems," Ph. D. Thesis, Department of Electrical and Computer Engineering, Concordia University, Québec, March 2005.

- [1.5] Semiconductor Equipment and Materials International, "SEMI F47-200 Specifications for semiconductor processing equipment voltage immunity", in SEMI Standards, www.semi.org, Mountain View, CA 2000.

- [1.6] Dong-Myung Lee: "A voltage sag supporter utilizing a PWM-Switched autotransformer," Ph. D. Thesis, School of Electrical & Computer Engineering Georgia Institute of Technology, Atlanta GA, April 2004.

- [1.7] Gerhard Linhofer, Philippe Maibach, and Francis Wong: "Power quality devices for short term and continuous voltage compensation", *International Power Quality Conference 2002*, Singapore, 2002.

- [1.8] Y. S. Kim, J. S. Kim and S. H. Ko: "Three-phase three-wire series active power filter, which compensates for harmonics and reactive power," *IEE Proceedings Electric Power Applications*, vol. 151, no. 3, pp. 276-282, May 2004.

- [1.9] Subhashish Bhattacharya: "High Power Active Filter Systems," Ph. D. Thesis, University of Wisconsin-Madison, 2003.

- [1.10] Zheng Zhou, "Simulation and Control of Active Filter," M. Sc. Thesis, Department of Electrical and Computer Engineering, University of Manitoba, Winnipeg-Manitoba, November 2003.

- [1.11] J. G. Nielsen, F. Blaabjerg, and N. Mohan, "Control strategies for dynamic voltage restorer compensating voltage sags with phase jump", in Proceedings IEEE Applied Power Electronics Conference and Expositions, APEC'01, vol. 2, pp. 1267-1273, 2001.

- [1.12] M. J. Newman, D. G. Holmes, J. G. Nielsen and F. Blaabjerg, "A dynamic voltage restorer (DVR) with selective harmonic compensation at medium voltage level," in *Conference Record IEEE-IAS Annual Meeting*, vol. 2, pp. 1228-1235, 2003.

- [1.13] E. K. K. Sung, S. S. Choi, and D. M. Vilathgamuwa: "Analysis of series compensation and DC-Link voltage controls of a transformerless selfcharging dynamic voltage restorer", *IEEE Transactions on Power Delivery*, vol. 19, pp. 1511-1518, 2004.

- [1.14] D. M. Vilathgamuwa, C. J. Gajanayake, P. C. Loh, and Y. W. Li, "Voltage sag compensation with Z-source inverter based dynamic voltage restorer," in Conference Record IEEE Industry Applications Conference, 41<sup>st</sup> Annual Meeting, vol. 5, pp. 2242-2248, 2006.

- [1.15] F. Mancilla-David and G. Venkataramanan, "A pulse width modulated AC link Unified Power Flow Controller," in *Proceeding of the 2005 IEEE Power Engineering Society Genera Meeting, PES-GM*, San Francisco, California, 2005.

- [1.16] P. Gamboa, J. F. Silva, S. Ferreira Pinto and E. Margato: "Predictive optima matrix converter and flywheel energy storage," *IEEE Industrial Electronics 35<sup>th</sup> Annual Conference, IECON'09*, pp. 759-764, Porto, Portugal, Nov. 2009.

- [1.17] B. Wang and G. Venkataramanan: "Dynamic voltage restorer utilizing a matrix converter and flywheel energy storage," *IEEE Transactions on Industry Applications*, vol. 45, pp. 222-231, Jan-Feb 2009.

- [1.18] Julio Cesar Rosas Caro, "Simple Topologies for power conditioners and FACTS controllers," *Tesis de Doctorado en Ciencias, CINVESTAV Unidad Guadalajara*, 2009.

### CHAPTER II

# Voltage Disturbances and Mitigation Devices

Nowadays, there is an increasing demand for high quality and reliable power. One important reason for that is that all electrical devices are prone to failure or malfunctioning when they are exposed to one or more power quality problems. The concept of power quality at distribution level refers to maintaining a near sinusoidal power distribution bus voltage at a rated magnitude and frequency.

This chapter introduces the concept of power quality, reviewing the common terms and the typical characteristics of some voltage disturbances. In addition, a brief comparison of previous work in power electronics-based equipment for voltage compensation is exposed.

#### 2.1 Power Quality Issues

The power quality term is commonly used to denominate the shortcomings present in transmission and distribution systems. This concept implies supply availability, reliability and voltage quality in the power supplied to the customers. Power quality degradation is inherently related to any failure of equipment due to deviations of the line voltage from its nominal characteristics, which often results in industrial process interruption causing substantial economic losses [2.1].

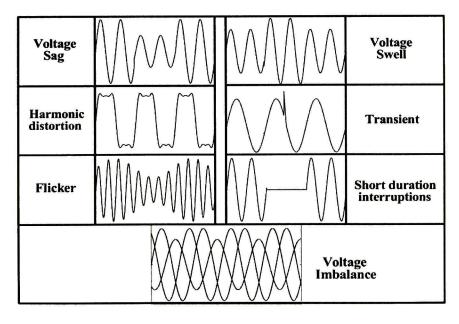

The principal phenomena concerned in power quality are [2.2]:

- Harmonics and other departures from the intended frequency of the alternating supply voltage

- Voltage fluctuations, especially those causing flicker

- Voltage dips and short interruptions

- Unbalanced voltages on three-phase systems

- Transient over-voltages, having some of the characteristics of high-frequency phenomena.

Fig 2.1 shows a general classification of power quality issues originated in the power distribution system and within the end-user. As in this thesis voltage based compensation is considered, the adverse effects of distribution system voltages are briefly revised in the next sections.

Figure 2.1. Sources of power quality problems

#### 2.1.1 Voltage disturbances in distribution systems

A few years back, the main concern of consumers of electricity was reliability of supply. However, actual sensitive loads and modern communications needs a reliable supply with high quality voltage, that means AC line voltage supply with a pure sine wave of fundamental frequency and at rated peak value. Achieving such power delivery conditions is very difficult in electric distribution systems because to all the failures generated within the system are associated problems of voltage variations and power interruptions. Unfortunately, at the present time most of the loads in the distribution system are not tolerant to large voltage fluctuations.

There are many ways in which the lack of quality power affects customers [2.3]. Voltage dips can cause loss of production in automated process, and can also force a computer system or data processing system to crash. Sustained overvoltage can cause damage to household appliances, industrial equipment failures due to insulation breakdown, magnetic

saturation, and resultant harmonic generation. Under-voltages may cause degradation in the performances of the loads such and induction motors, light bulbs, etc. Voltage imbalance can cause temperature rises in motors. Harmonics can cause losses and heating in transformers, electromagnetic interference and acoustic noise. In conclusion, it is crucial to maintain a power quality high standard. Thus, is necessary to have a vast knowledge of the actual phenomena which may cause the problems. The main voltage disturbances are summarized in Figure 2.2.

Among various power quality problems, the majority of events are associated with either a voltage sag or a voltage swell, and they often cause serious power interruptions.

Voltage sag is a momentary decrease of the voltage rms value with the duration of a half a cycle up to many cycles. According to the Canadian Electrical Association (CEA) and the Electric Power Research Institute (EPRI) surveys, a voltage sag is defined as being less than 92% and 90% of nominal voltage, respectively [2.4]-[2.6]. For the CEA, a swell condition can be defined as the voltage level greater than 104% of nominal voltage, while that of the EPRI is 110%. In the National Power Laboratory (NPL) survey, the voltage range of 106% to 110% of nominal voltage is considered to be a voltage swell event. A revision of the data collected concerning on voltage disturbances indicates a predominant presence of voltage sags in electric power systems. In [2.7] it can be seen that voltage sags events defined by 0% to 87% of nominal voltage comprise 68% of power disturbances registered by the NPL and 93.3% of total events registered by the EPRI.

Figure 2.2. Voltage disturbances

Besides the above surveys, many papers have reported power quality surveys. The data presented in [2.8] indicates that most of faults are single-line to-ground fault, where 2% of all faults correspond to voltage sags with the remaining amplitude down to 40-50% of nominal value, and that most of these faults last for less than 2 seconds. Long-term interruptions (2 seconds to ten minutes) proved to be rare, accounting for an additional 4% of all faults. Similar data have also been recorded in a survey of Canadian power systems in 1997 [2.9]. According to [2.10], switching power supplies, industrial control relays, contactors, solenoids, adjustable-speed motor drives and thyristor controlled rectifiers are all susceptible to short term voltage sags.

#### 2.1.2 Harmonic distortion

Another power quality issue which recently has receives considerable attention are the power systems harmonics. The increasing use of industrial systems microprocessor based, utility line-connected solid-state power converters, etc., has prompted growing concern over this aspect. A widely definition uses for harmonics establish that: "harmonics are sinusoidal voltages or currents having frequencies that are integer multiples of the frequency at which the supply system is designed to operate" [2.11].

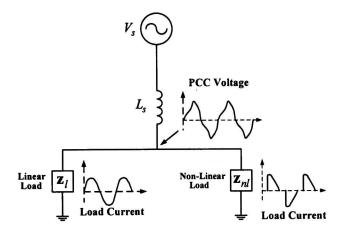

Ideally, three-phase voltages are balanced and with constant rms (root mean square) value and frequency in each phase. Thus, when an electric load is linear, the voltage and currents are perfect sinusoids. However, the popularity of electronic components and other kind of non-linear loads makes these waveforms become distorted. A common non linear load is an ac induction motor drive, in which the most significant harmonic currents injected into the ac supply include the 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, and 13<sup>th</sup> harmonics. When source inductance is taken into account, circulation of harmonic currents in the ac system results in voltage distortion at various points in the ac system. The distorted voltage waveform affects the operation of both the nonlinear load and other linear and nonlinear loads connected to the same bus, or PCC, or adjacent buses, as Fig 2.3 shows.

Harmonic voltages impact on power systems consists in the generation of harmonic currents. When these currents flow through magnetic devices such as energy transformers, motors, etc., can generate excess heat, additional losses and shorten devices' lifetime. On the other hand, harmonics or interharmonics with frequencies within hearing range, can produce interferences on telephone lines via inductive coupling, as well as over-current relays and power brakers malfunctioning due to skin effect [2.12]-[2.13]. Additionally to problems mentioned above, there exists other kind of events related to harmonics that have impacts in power system capacitors. Although a capacitor is not a harmonic source, it can provide the loop to harmonic currents, creating the conditions for repetitive over-voltages in capacitor banks increasing the temperature, accelerating age, and even explode. In

addition, if capacitors are applied at locations having large adjustable-speed drives, the potential to resonance problems must be considered.

Figure 2.3. Voltage harmonics propagation

#### 2.1.3 Voltage imbalance

In three-phase systems, load imbalance could be caused by unevenly distributed singlephase load or by balanced three-phase load running at a fault condition, such as phase open or short fault.

An unbalanced three-phase voltage source applied to three-phase motors causes the appearance of a negative sequence current which increases the motor's internal losses, heating it up. If the motor is running at near rated loads, then this could cause the motor overheat and could be severely damaged. Table 2.1, displays the effects of unbalanced phase voltages applied to class A and class B three-phase motors running at rated loads. In addition to motor damage, voltage imbalance in three phase systems can cause malfunctioning of the electronic equipment connected [2.16].

|                                | 17 | 1.000 |     |     |

|--------------------------------|----|-------|-----|-----|

| Voltage Imbalance (%)          | 0  | 2     | 3.5 | 5   |

| Negative sequence current (%)  | 0  | 15    | 27  | 38  |

| Increase in losses (%)         | 0  | 9     | 25  | 50  |

| Class A Temperature raise (°C) | 60 | 65    | 75  | 90  |

| Class B Temperature raise (°C) | 80 | 85    | 100 | 120 |

Table 2.1. Effect of voltage imbalance on motors at rated load

## 2.2 Power Quality Guidelines and Standards

Currently, several engineering organizations and standard bearers in several parts of the world are spending a large amount of resources to generate power quality standards. The American National Standards Institute (ANSI) and the Institute of Electrical and Electronics Engineers (IEEE) have established several guidelines concerning major power quality problems.

Regarding voltage tolerance, it depends on the specific application. That is the main reason why it is almost impossible to develop guidelines and operative standards that can encompass acceptable limits regarding voltage levels in distribution systems. Companies that build sensitive equipment should provide acceptability curves for the equipment they produce. Anyhow, curves as CBEMA [2.17], and Information Technology Industry Council (ITIC) curve [2.18], Fig. 2.4, suggest a guideline for voltage quality in power distribution systems serving main computers, and it can become an industry reference for acceptable voltage tolerance. This curve specifies the voltage dip magnitude and the duration of the voltage sag for 120 V single-phase applications. This curve is useful for providing general insight into acceptable voltage quality.

Figure 2.4 ITIC curve

About the harmonic distortion presented in distribution systems, several organizations as CENELEC (European Committee for Electrotechnical Standardization), IEC (International Electrotechnical Commission) and IEEE-IAS (Institute of Electrical & Electronics Engineering, Industry Application Society), have established professional committees to investigate the harmonic distortion impacts. Among the standards developed to supervise

harmonic distortion issues, the IEEE-519 guide for evaluation of the power system harmonic level issued in 1992 [2.15], is the most comprehensive.

Summaries of the acceptable amount of harmonic distortion presented in distribution systems are given in Table 2.2.

| Power system voltage level        | *Dedicated Power System | General Power<br>System |

|-----------------------------------|-------------------------|-------------------------|

| Medium Voltage<br>2.4 kV to 69 kV | 8%                      | 5%                      |

| High Voltage<br>115 kV and above  | 1.50%                   | 1.50%                   |

Table 2.2. Voltage distortion guidelines for power systems

Where voltage distortion percentage is defined as,

$$\%_{distortion} = \left(\sqrt{\frac{\sum_{h=2}^{\infty} V_h^2}{V_I^2}}\right) 100 \tag{2.1}$$

where  $V_h$  is the amplitude of the  $h^{th}$  harmonic voltage and  $V_I$  is the amplitude of the fundamental voltage.

Finally, referring to voltage imbalance, there are several ways to define it. One definition is given in NEMA standard MG1 [2.14], where voltage imbalance is expressed as a percentage according to,

$$\%_{unbalance} = \frac{3(V_{a,b,c \max} - V_{a,b,c \min})}{V_a + V_b + V_c} 100$$

(2.2)

where  $V_{a,b,c\,\text{max}}$  is the maximum rms phase voltage, and  $V_{a,b,c\,\text{min}}$  is the minimum rms phase voltage. NEMA MG1 sets a voltage imbalance guideline of no more than 1% in order to prevent damage to sensitive loads.

<sup>\*</sup> A dedicated power system is one supplying only converters or loads that are not affected by voltage distortion.

## 2.3 Power Electronics Applications in Power Systems

The evolution taking place in the electricity supply industry is heading toward maximizing existing transmission and distribution resources, with high levels of stability and power quality. This trend points in the direction of power electronics [2.19]. Two kinds of power electronics applications have gained importance in power systems, and now are already well defined: active and reactive power control, and power quality improvement.

The first application area is for arrangements known as Flexible Alternating Current Transmission Systems (FACTS), where the latest power electronic devices and methods are used to control the transmission side of the electric network. The second application area is for devices known as Custom Power System (CUPS), which focus on the distribution system supplying the energy to end-users and is a technology created in response to reports of poor quality of supplied energy.

#### 2.3.1 FACTS controllers

The FACTS concept was introduced by Narain G. Hingorani [2.20]-[2.21] at the end 80's, to face with the requirement of improving the transmission system operation. According to IEEE, FACTS controllers are defined as [2.22]: Alternating current transmission systems which use power electronics-based static compensators to improve the controllability and increase the power transfer capability.

FACTS controllers' operational principle is based on the modification of electric system parameters such as: transmission line impedance, voltage magnitude and phase angle in one system node. Some of the advantages achieved by FACTS controllers are [2.23]-[2.24]:

- Higher control on power flow.

- Voltage regulation on system nodes.

- Increase the system transient stability margins.

- Damp system oscillations, preventing equipment damage and increasing power transmission capability.

- Allow reliable interconnections between companies and neighbor regions.

- High power flow transfer capability between controlled interconnected systems.

According to the connection, FACTS controllers can be divided into [2.25]:

- Series connected devices.

- Static synchronous series compensator (SSSC).

- ◆ Thyristor switched series capacitor (TSSC).

- ◆ Thyristor switched series reactor (TSSR).

- Shunt connected controllers

- Static synchronous generator (SSG).

- Static var generator (SVG).

- Static compensator (STATCOM).

- Thyristor controlled reactor (TCR).

- Thyristor switched capacitor (TSC).

- Combined controllers

- Unified power flow controller (UPFC)

- Shift phase transformer

Each FACT device is designed to carry out specific control functions within the power systems. At present, an extensive bibliography related FACTS technology does exist [2.25]-[2.27].

## 2.3.2 Custom Power System (CUPS) devices

As with FACTS devices in transmission systems, power electronics devices can be applied to the power distribution systems to increase reliability and the quality of power supplied to the customers [2.28] –[2.29]. The devices applied to the power distribution systems for the benefit of customers are called Custom Power Systems.

Custom power devices are basically a compensating type, used for active filtering, load balancing power factor correction and voltage regulation. These devices usually include VSCs controlled by various control strategies and depending on the topology can be divided in three major types: current, voltage and combined compensation. Selected devices pertinent to CUPS technology are:

- Distribution Static Compensators (DSTATCOM) [2.30]. This device can complete current compensation, power factor correction, harmonic filtering, load balancing and also voltage regulation.

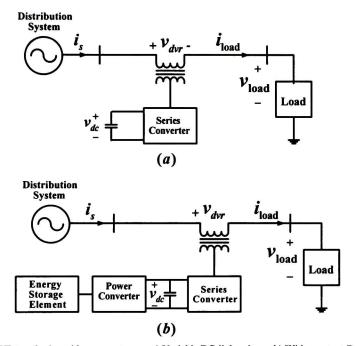

- Dynamic Voltage Restorer (DVR) [2.31]. The DVR is a device implemented in low and medium voltage to perform voltage based compensation as voltage harmonics filtering, voltage regulation and balancing. The conventional DVR topology is constituted by a passive storage element feeding a voltage inverter through a DC-link. In recent years the DVR has gained acceptance among industrial consumers as an efficient and economic solution to mitigate voltage disturbances on power feeders. However, despite its operational advantages exhibited, DVR capabilities are conditioned by the energy storage device used. As the main objective of this thesis is to develop a novel DVR topology, more details about DVR operational principle, configuration and control techniques are presented in Chapter V.

Unified Power Quality Conditioner (UPQC) [2.32]-[2.33]. The combination of current and voltage compensation in distribution systems is referred to as the UPQC. The conditioning functions of the UPQC are shared by the series and shunt compensators; while its series compensator performs harmonic isolation between supply and load, voltage regulation and voltage flicker/imbalance compensation, the shunt compensator performs harmonic current filtering and negative sequence balancing as well as regulation of the DC-link voltage.

#### 2.4 AC-link Power Converters

The second generation of FACTS controllers is based mainly on DC-link voltage source converters [2.34]-[2.35]. However, some advances on AC-AC converter-based controllers have appeared recently [2.36]-[2.40], being a novel choice for power conditioning and power flow control.

According to the operating principle, the AC-AC converters can be classified as follows [2.36]:

- Direct AC-AC converters.

- AC-link converters.

- AC-DC-AC converters.

Since the AC-DC-AC converter requires a DC-link it will not be considered as part of the AC-Link technology and therefore will not be analyzed here. The other two types of configurations are briefly presented, emphasizing their main characteristics.

## 2.4.1 Direct AC-AC converters

Direct AC-AC converters belong to the static frequency changers devices. The term static frequency changer is applied to electric circuits integrated by semiconductor switches and able to convert electric power with a frequency  $\omega_I$ , at the input supply system terminals, to electric power with a frequency  $\omega_2$ , at the load terminals. Static frequency changers can control frequency and voltage magnitude at load terminals without the need of transformers, just based on the static power switches control. Thus, load voltage is synthesized from segments of input voltage.

According to the switches' technology they can be divided in:

• Naturally Commutated Cycloconverters (NCC).

A three-phase to three-phase NCC is illustrated in Fig. 2.5 [2.41]. It requires naturally commutated back-to-back three-phase inverters for each output phase. Depending on the load current direction, the positive or negative inverter will be switched on. In each inverter, the operational mode (rectifier or inverter modes) is determinate by the output voltage sign.

Employing NCCs output voltage and frequency can be controlled but it is not possible to regulate input power factor. Traditionally, NCCs have been applied as drivers for high power AC motors, where no other kind of drive can be used. Concerning its drawbacks, next limitations can be pointed out:

- Output frequency of approximately 0.33 of input frequency

- Complex control strategy

- High number of thyristors

- Output voltages and input currents with a high level of harmonic content

- Input power factor depending on load power factor.

Figure 2.5. Three phase-to-three phase NCC

#### • AC-AC Matrix converters.

Matrix converter devices are based on the forced-commutation principle, for which utilize power bidirectional switches commutating at high frequencies. The matrix converter denomination is due to its structure resembles a power cells matrix with

"m" input lines and "n" output columns, as can be seen on Fig 2.6. The matrix converter belongs to the *Unrestricted Frequency Changers* family, since the output frequency is only restricted by practical aspects. On the other hand, a major restriction imposed to this converter is related to its transfer voltage ratio, which is limited to 0.866 times the input voltage. Another important limitation in matrix converter implementation is the lack of commercially available power bidirectional switches; however, this disadvantage can be overcome through the use of unidirectional switches configurations. By connecting a LC passive filter at the input terminals of the converter, input current harmonics are attenuated and the commutation process is improved.

Three remarkably aspects make this kind of technology very attractive:

- i) Unrestricted output frequency

- ii) Input current with low harmonic content

- iii) Controllable input power factor

Due to the matrix converter advantages, it is a good option for the following applications:

AC motor driver in areas where physical size is to be considered or operation under adverse environments is required.

Link-converter between non-conventional electric sources and the AC power supply system.

- Interconnection of power systems with different frequencies.

- Voltage disturbances compensation in distribution systems.

#### 2.4.2 AC-link converters

AC-link converters are converters without frequency change capability but with simpler topologies than AC-AC direct converters. They can be transformers assisted or not. The most important AC-link converters' applications are focused on power flow control and voltage regulation. The AC-link converter principle is the high frequency chopping of an AC signal with constant duty cycle, in this way the converter can modifies the amplitude of the fundamental frequency component. The output signal contains such modified component plus high frequency components due to the switching.

Figure 2.6. Three phase-to-three phase matrix converter

Based on o the well known DC-DC energy conversion strategy, AC-link converters have emerged as a novel solution for compensation voltage applications. For instance: buck, boost and buck-boost topologies. Fig 2.7 shows a one-phase AC-link buck and boost converters. In these topologies AC-link converters consists of two static power switches per phase and passive elements such as inductors and capacitors, used for increasing or decreasing voltage magnitudes. Since in AC-link converters current flows in both directions, bidirectional switches have to be taken into account. In Fig. 2.7, switches S1 and S2 operate in a complementary way, being necessary to provide a dead-time between switching operation to avoid the risk of short-circuits.

Figure 2.7. AC-AC voltage regulator topologies

For voltage compensation purposes with the previous topologies, a transformer would be necessary to reject steps down and voltage swells variations. Then the topology with the AC-link buck type converter with a transformer at the output terminals would be similar to the traditional DVR configuration just replacing the energy storage device and the DC-AC

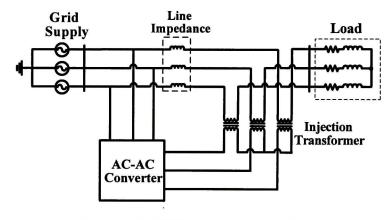

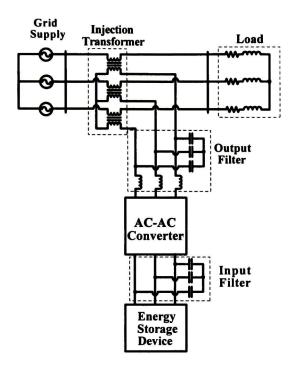

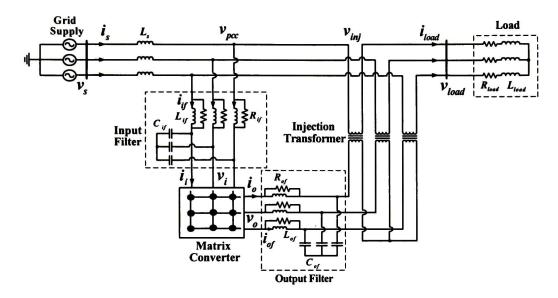

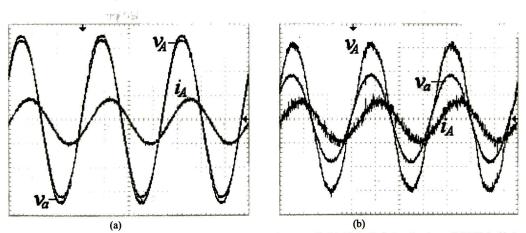

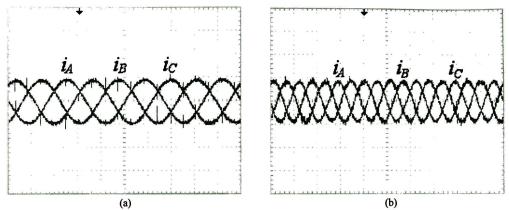

inverter with the AC-link converter. In this way, by reducing the number of elements, the overall cost of the system is reduced as well. Along with the topologies presented, other topologies with AC-link converters have been proposed for voltage sags compensation [2.19], [2.42]-[2.43].