2T-801-551 200-7014

### Centro de Investigación y de Estudios Avanzados del Instituto Politécnico Nacional Unidad Guadalajara

# Adaptación de la metodología de paralelización de bucles en el modelo del politopo para la implementación de algoritmos en GPUs

Tesis que presenta:

**Daniel Robles Valdez**

para obtener el grado de:

Maestro en Ciencias

en la especialidad de:

Ingeniería Eléctrica

CINVESTAVIPN ADQUISICION LIBROS

Director de Tesis Dr. Deni Librado Torres Román CLASIF., CTCO705 ADQUIS., CT - 201-551 FECHA: 27 - 10 - 1014 PROCED., DOU- 2014

# Adaptación de la metodología de paralelización de bucles en el modelo del politopo para la implementación de algoritmos en GPUs

## Tesis de Maestría en Ciencias Ingeniería Eléctrica

Por:

**Daniel Robles Valdez**

Ingeniero en Electrónica

Instituto Tecnológico de Sonora 2006-2011

Becario de Conacyt, expediente no. 263584

Director de Tesis

Dr. Deni Librado Torres Román

CLASIF., CTOO705 ADQUIS., CT - 201-551 FECHA: 27 - 10-1014 PROCED., DON- 2014

# Adaptación de la metodología de paralelización de bucles en el modelo del politopo para la implementación de algoritmos en GPUs

## Tesis de Maestría en Ciencias Ingeniería Eléctrica

Por:

Daniel Robles Valdez

Ingeniero en Electrónica

Instituto Tecnológico de Sonora 2006-2011

Becario de Conacyt, expediente no. 263584

Director de Tesis Dr. Deni Librado Torres Román

## Resumen

Esta tesis presenta una introducción al lenguaje de programación CUDA C para la implementación de algoritmos en GPU's. Explica como es la interacción entre el CPU y el GPU, la asignación de tareas en los procesadores y manejar los diferentes tipos de memoria de un GPU.

Se presenta como modelar bucles anidados empleando el modelo del politopo, el criterio de legalidad de una transformación unimodular y como construir la matriz de transformación a partir de las dependencias de datos.

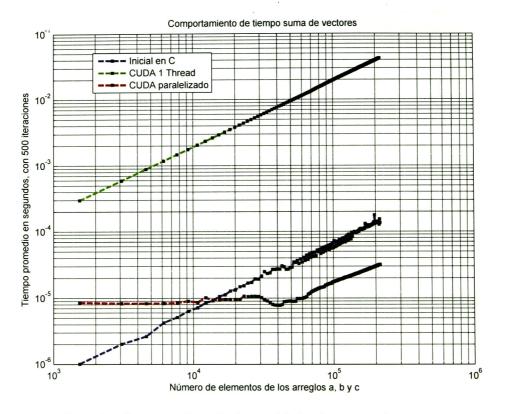

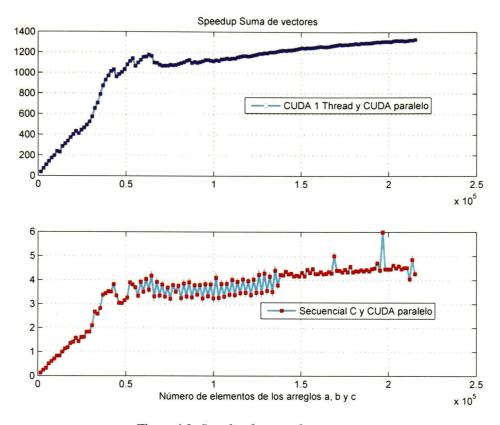

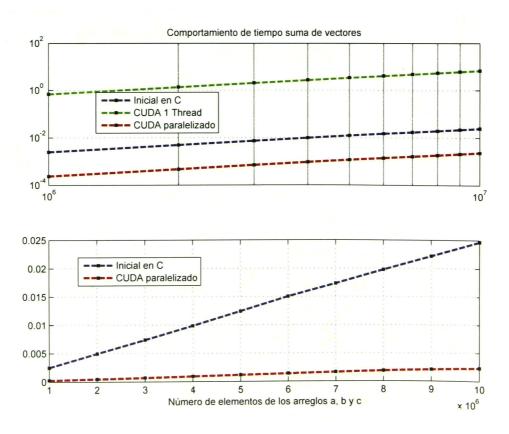

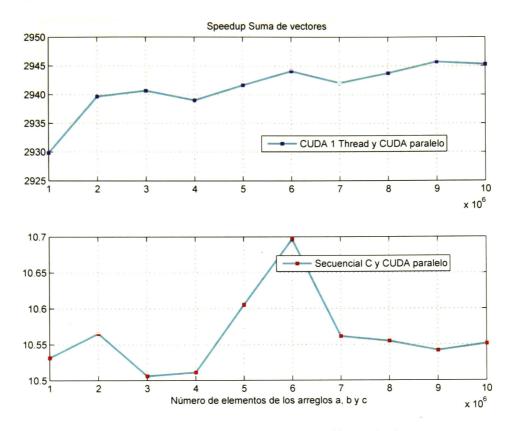

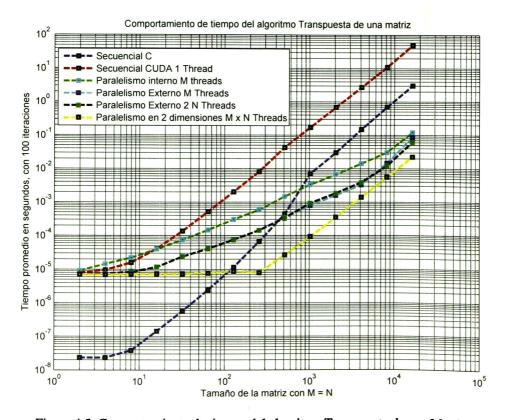

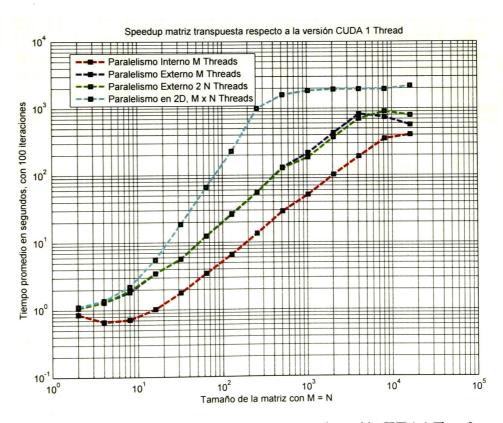

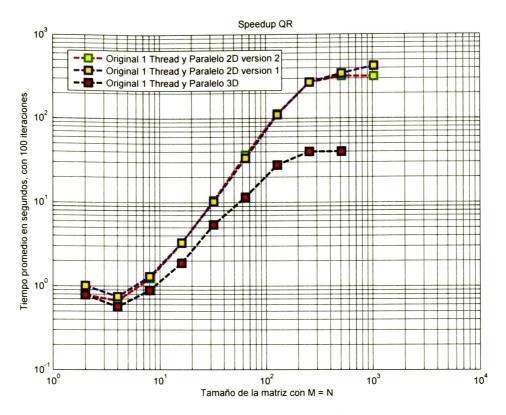

Se analizan e implementan tres algoritmos: suma de vectores, matriz transpuesta y descomposición QR. Se comparan los resultados obtenidos de las versiones secuenciales con las versiones paralelas en CUDA C y se analiza el gasto de memoria de los algoritmos para diferentes tamaños de matrices o vectores.

Con las adaptaciones a la metodología de paralelización de bucles anidados, se obtuvo una versión de la descomposición QR, en donde se reduce la memoria requerida y los tiempos de ejecución resultantes.

Con la arquitectura de CUDA se reduce significativamente el tiempo de ejecución para algoritmos paralelizados que procesan un alto volumen de datos.

## **Abstract**

This thesis presents an introduction to the CUDA C programming language for implementing algorithms on GPU 's. Explain how is the interaction between the CPU with the GPU, the allocation of tasks to processors and handle different types of memory in a GPU.

Furthermore, a strategy for modelling nested loops, as well as, a criterion of legality of a unimodular transformation, and how to build a transformation matrix from data dependences are presented.

We analyzed and implemented three algorithms: vector sum, transposed matrix and QR decomposition. The results of sequential and parallel CUDA C versions are compared and memory usage of algorithms for different size matrices or vectors are analyzed.

With adjustments to the methodology of parallelization nested loops, a version of the QR decomposition, where reduced memory requirements, and resulting execution times was obtained.

With this CUDA architecture, a significant time reduction is obtained for parallelized algorithms which process high volume of data.

# **Agradecimientos**

- A Dios por sus cuidados y múltiples bendiciones.

- A mis padres por apoyarme siempre en cada etapa de mi vida.

- A mi novia Raquel Esperón por acompañarme y por su cariño.

- A mi asesor Dr. Deni Librado Torres Román por su apoyo y dirección.

- Al Dr. Manuel E. Guzmán Rentería por compartir sus ideas, conocimientos y consejos.

- A mis amigos y compañeros de generación: Laura, Alberto, Joaquín, Benjamín y Gustavo, por la buena convivencia y su apoyo.

- A David Castro y a Ángel Jovany por compartir sus ideas y conocimientos.

- Al Consejo Nacional de Ciencia y Tecnología por el apoyo económico.

# **Contenido**

| R | esume                    | en                               |                                                   | v   |

|---|--------------------------|----------------------------------|---------------------------------------------------|-----|

| A | bstrac                   | et                               |                                                   | VII |

| A | grade                    | cimient                          | entos  Ix  Ix  Ix  Ix  Ix  Ix  Ix  Ix  Ix  I      |     |

| C | onteni                   | ido                              |                                                   | 1   |

| 1 | Intr                     | oducció                          | on .                                              | 1   |

|   | 1.1.                     | Introd                           | ucción .                                          | 1   |

|   | 1.2.                     | Motiva                           | ación                                             | 1   |

|   | 1.3.                     | Objetivos                        |                                                   |     |

|   | 1.4.                     | Perspe                           | ectiva de los capítulos                           | 2   |

| 2 | CUI                      | OA y Gl                          | PU                                                | 5   |

|   | 2.1. Introducción a CUDA |                                  |                                                   | 5   |

|   |                          | 2.1.1.                           | Modelo de programa en CUDA                        | 5   |

|   |                          | 2.1.2.                           | Jerarquía de hilos de ejecución                   | 6   |

|   |                          | 2.1.3.                           | Ejemplo de programa en CUDA: Suma de dos vectores | 7   |

|   |                          | 2.1.4.                           | Medición de tiempos de ejecución en el GPU        | 11  |

|   | 2.2.                     | Arquit                           | ectura GPU                                        | 12  |

|   |                          | 2.2.1.                           | Clasificación de sistemas de cómputo              | 12  |

|   |                          | 2.2.2.                           | Características de los GPU                        | 12  |

|   |                          | 2.2.3.                           | Multiprocesadores                                 | 13  |

|   |                          | 2.2.4.                           | Jerarquía de memoria .                            | 16  |

|   | 2.3.                     | Buenas prácticas de programación |                                                   | 22  |

|   |                          | 2.3.1.                           | Utilización de los multiprocesadores              | 22  |

|   |                          | 2.3.2.                           | Concurrencia host/device                          | 25  |

|   |                          | 2.3.3.                           | Optimizaciones de memoria                         | 25  |

|   | 2.4.                     | Resum                            | nen del capítulo                                  | 27  |

II CONTENIDO

| 3 | Trai | ısforma                  | ción de algoritmos con bucles anidados         | 29 |

|---|------|--------------------------|------------------------------------------------|----|

|   | 3.1. | Antece                   | edentes matemáticos                            | 29 |

|   |      | 3.1.1.                   | Vectores y matrices                            | 29 |

|   |      | 3.1.2.                   | Reducción de matrices a la forma escalonada    | 30 |

|   |      | 3.1.3.                   | Solución de sistemas de desigualdades lineales | 31 |

|   | 3.2. | Modela                   | ado de bucles anidados                         | 31 |

|   | 3.3. | Depend                   | dencia de datos                                | 32 |

|   | 3.4. | Transfo                  | ormaciones unimodulares                        | 34 |

|   |      | 3.4.1.                   | Matrices unimodulares                          | 34 |

|   |      | 3.4.2.                   | Legalidad de una transformación unimodular     | 34 |

|   |      | 3.4.3.                   | Procedimiento                                  | 35 |

|   |      | 3.4.4.                   | Transformaciones elementales                   | 39 |

|   | 3.5. | .5. Tipos de paralelismo |                                                | 42 |

|   |      | 3.5.1.                   | Introducción                                   | 42 |

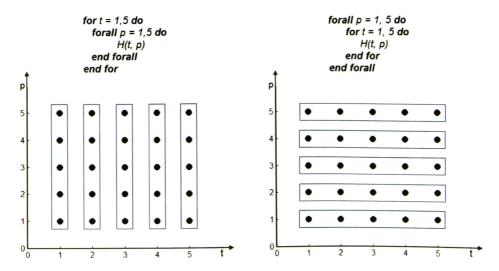

|   |      | 3.5.2.                   | Paralelización de bucles internos              | 43 |

|   |      | 3.5.3.                   | Paralelización de bucles externos              | 44 |

|   | 3.6. | Resum                    | en del capítulo                                | 45 |

| 4 | Imp  | lementa                  | ción de algoritmos en CUDA                     | 47 |

|   | 4.1. | Suma o                   | de vectores                                    | 47 |

|   |      | 4.1.1.                   | Versión secuencial                             | 47 |

|   |      | 4.1.2.                   | Versión Paralela                               | 48 |

|   |      | 4.1.3.                   | Análisis de resultados                         | 50 |

|   | 4.2. | Transp                   | uesta de una matriz                            | 56 |

|   |      | 4.2.1.                   | Transpuesta de una matriz                      | 56 |

|   |      | 4.2.2.                   | Versión secuencial                             | 56 |

|   |      | 4.2.3.                   | Versión con paralelismo externo                | 57 |

|   |      | 4.2.4.                   | Versión con paralelismo interno                | 60 |

|   |      | 4.2.5.                   | Versión con paralelismo en 2-dimensiones.      | 61 |

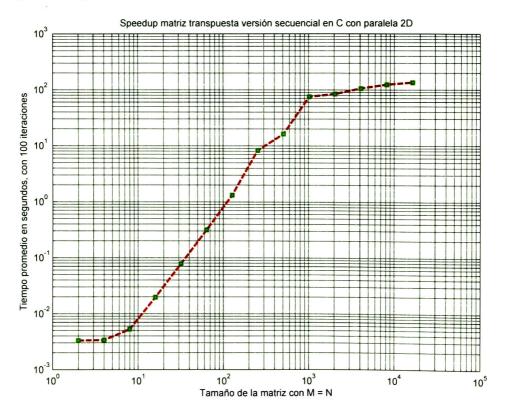

|   |      | 4.2.6.                   | Análisis de resultados                         | 62 |

|   | 4.3. | Descor                   | mposición QR                                   | 65 |

|   |      | 4.3.1.                   | Versión original.                              | 66 |

|   |      | 4.3.2.                   | Transformación del algoritmo                   | 66 |

|   |      | 4.3.3.                   | Versión paralela.                              | 71 |

|   |      | 4.3.4.                   | Implementación en CUDA                         | 76 |

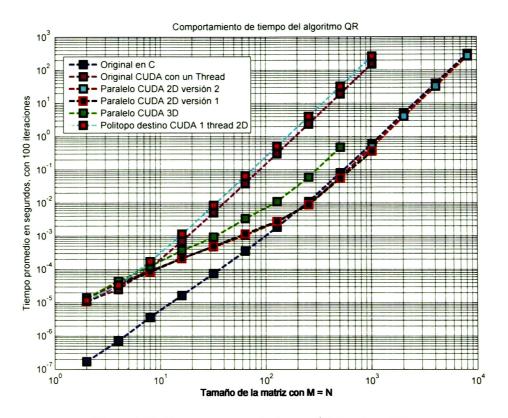

|   |      | 4.3.5.                   | Análisis de resultados                         | 77 |

|   | 4.4. | Resum                    | nen del capítulo                               | 81 |

| 5 | Con  | clusion                  | es y trabajo futuro                            | 83 |

|   |      | Conclu                   |                                                | 83 |

|   |      |                          | o futuro                                       | 84 |

|   |      |                          |                                                |    |

| CONTENIDO | III |

|-----------|-----|

|           |     |

| Bibliografía                                           | 85  |  |

|--------------------------------------------------------|-----|--|

| A Programas CUDA C                                     | 87  |  |

| A.1. Programa Ejemplo, suma de vectores de 5 elementos | 88  |  |

| A.2. Ejemplo de manejo de memoria Texture 3D           | 91  |  |

| A.3. Ejemplo de manejo de memoria Surface 2D           | 93  |  |

| Glosario                                               | 95  |  |

| Acrónimos                                              | 99  |  |

| Lista de figuras                                       | 100 |  |

| Lista de tablas                                        | 102 |  |

### Capítulo 1

## Introducción

#### 1.1. Introducción

Estamos en la era dorada del computo GPU (graphics processing unit). Desde la introducción de CUDA (Compute Unified Device Architecture) en 2007, más de 100 millones de computadoras con GPUs compatibles con CUDA han sido construidos y utilizados alrededor del mundo. Como resultado, muchos investigadores tienen ahora que reformular sus modelos computacionales e invertir en software para crear aplicaciones de alto rendimiento basados en esta tecnología [1].

Es sabido, que muchas aplicaciones en ciencia e ingeniería, en donde se procesa un gran volumen de datos, pasan una parte considerable de su tiempo de ejecución en el procesamiento de bucles. Por tal motivo, es pertinente desarrollar técnicas en donde se modifique el código para que se ejecute, en paralelo, la mayor cantidad de iteraciones de los bucles.

#### 1.2. Motivación

Actualmente en el área de procesamiento digital de señales, así como en otras áreas de la ingeniería, como por ejemplo: procesamiento de audio, formación de imágenes médicas y modelado estadístico, entre otras, se están empleando en gran medida las GPU's. Por tal motivo, existe una gran interés en mejorar el nivel de desempeño (uso de memoria, uso de procesadores y tiempo de ejecución) de diferentes algoritmos [1].

En lo general, en el área de procesamiento de señales, audio e imágenes, se están implementando algoritmos que realizan el cálculo de la FFT (Fast Fourier Transform) a larga escala, el reconocimiento automático del habla y en la reconstrucción de imágenes tomográficas en 3D, sólo por mencionar algunas.

En lo particular, en CINVESTAV (Centro de Investigación y de Estudios Avanzados) Unidad Guadalajara departamento de telecomunicaciones, se han hecho varios esfuerzos que han producido trabajos de investigación [2], [3] y [4]. Los cuales aplican una metodología para la paralelización de algoritmos usando el modelo del politopo. Por lo tanto, se cuenta con una metodología de paralelización de algoritmos; la cual, se encuentra orientada hacia una implementación física en términos de un arreglo sistólico de procesadores.

Lo cual deja de manifiesto que el área del computo paralelo de alto desempeño no ha sido explorado, abriéndose con ello una amplia variedad de posibles soluciones usando herramientas orientadas a software. Con las cuales, se disponga de códigos paralelos en sentido estricto o matemático para su ejecución sobre una GPU, empleando las herramientas de CUDA C, convirtiéndose esta tarea en un gran reto.

#### 1.3. Objetivos

Adaptar la metodología de paralelización de bucles, empleado en el modelo del politopo, con la finalidad de lograr la implementación de algoritmos sobre GPU's utilizando el lenguaje CUDA C.

Los objetivos particulares son los siguientes:

- Describir aspectos teóricos y prácticos para el manejo de GPU's como un coprocesador paralelo.

- Describir aspectos teóricos y prácticos en la utilización del lenguaje CUDA C como herramienta para el manejo de las GPU's.

- Introducir bases teóricas para la transformación de algoritmos que poseen bucles anidados.

- Modelar un algoritmo secuencial que realiza la descomposición QR transformandolo a su versión paralela, a través de matrices de transformación unimodulares.

- Proponer alternativas de estructuración del código para el buen manejo de los procesadores de una GPU.

- Establecer buenas prácticas, que permitan el uso eficiente de los recursos (memoria global y procesadores) de una GPU.

#### 1.4. Perspectiva de los capítulos

En el capítulo 2 se presenta una introducción al lenguaje de programación CUDA C para la implementación de algoritmos en GPU's. Se explica como es la interacción entre el CPU (Central Processing Unit) con el GPU, la asignación de tareas en los procesadores y manejar los diferentes tipos de memoria de un GPU. Además, se presenta una sección con buenas prácticas de programación en CUDA.

3

El capítulo 3 inicia con los antecedentes matemáticos para modelar bucles anidados en el modelo del politopo. Presenta el criterio de legalidad de una transformación unimodular y como construir la matriz de transformación a partir de las dependencias de datos. Finalmente, aborda los tipos de paralelismo interno y externo.

En el capítulo 4 se analizan e implementan en CUDA C tres algoritmos: suma de vectores, matriz transpuesta y descomposición QR. Se comparan los resultados obtenidos de las versiones secuenciales con las versiones paralelas en CUDA y se analiza el gasto de memoria de los algoritmos para diferentes tamaños de matrices o vectores.

El capitulo 5 presenta las conclusiones y el trabajo futuro.

### Capítulo 2

# **CUDA y GPU**

#### 2.1. Introducción a CUDA

#### 2.1.1. Modelo de programa en CUDA

Un programa en CUDA consiste en la ejecución de código fuente en el host (CPU con su memoria) y en el device (GPU con su memoria). El device es manejado por funciones especiales de CUDA C que son escritas en el código del host, por lo que el device se puede ver como un esclavo del host.

El compilador nvec (NVIDIA C compiler) identifica y separa el código que se requiere ejecutar en el device del código del host. El código host es compilado y es ejecutado por un proceso ordinario en el CPU, este puede ser escrito en lenguaje estándar C/C++. El código device puede escribirse usando C extendido con identificadores para etiquetar funciones que se ejecutarán en el GPU, llamadas funciones kernel, y sus estructuras de datos asociadas[5]. Los identificadores para diferenciar las funciones del host y del device se muestran en la tabla 2.1. Si no se coloca un calificador a una función, el compilador la asociará a una función que se ejecutará en el host [6].

La secuencia básica de un programa en CUDA es la siguiente:

- 1. Generar los datos en el host.

- 2. Asignar memoria en el device.

- 3. Enviar los datos del host hacia el device.

- 4. Ejecutar la función kernel para el procesamiento de los datos.

- 5. Recolectar los datos procesados, realizando una copia del device al host.

- 6. Liberar toda la memoria utilizada en el host y en el device.

| Calificador | Ejecutado en: | Puede ser llamado desde |  |

|-------------|---------------|-------------------------|--|

| _device_    | Device        | Device                  |  |

| _global_    | Device        | Host                    |  |

| _host_      | Host          | Host                    |  |

Tabla 2.1: Identificadores de funciones.

Uno de los retos en la programación en CUDA es repartir las tareas entre el device y el host, de tal manera que nuestro programa completo se ejecute en la menor cantidad de tiempo. Para determinar que partes de código deben ser ejecutados por el host o por el device, es necesario examinar la dependencia de datos, que en ocasiones, resulta algo complicado. Paralelismo se refiere a la propiedad de un programa, mediante el cual, muchas operaciones aritméticas se pueden realizar de manera segura y de manera simultánea en las estructuras de datos.

Por lo que el código secuencial que exhibe poco o nada de paralelismo debe ser ejecutado en el *host*, mientras que el código que exhibe el mayor paralelismo debe ser ejecutado en el *device*.

#### 2.1.2. Jerarquía de hilos de ejecución

Para hablar de como CUDA y su modelo de programación puede explotar el paralelismo existente en un programa, es necesario primero establecer la terminología básica que se va a estar empleando en el desarrollo de esta sección y en las siguientes.

Llamaremos lanzamiento de kernel, a la ejecución de una función en el device con el calificador \_global\_. Al lanzar una función kernel, automáticamente se crean un conjunto de hilos de ejecución que llamaremos threads. En cada uno de los threads que se creen, se va a tener una copia del cuerpo de la función kernel, es decir, se van a ejecutar las mismas instrucciones, la diferencia es que los datos utilizados en el procesamiento podrán ser diferentes.

Cada thread tiene su identificador asociado llamado threadIdx, el cual puede ser de 1, 2 o hasta 3 dimensiones. Mismo que puede ser útil para referenciar diferentes localidades de memoria del device. ThreadIdx es una variable tipo uint3 que contiene tres campos de tipo entero no signado, los cuales determinan su posición en las 3 dimensiones.

Los *threads* son el nivel inferior en la jerarquía, seguidos por el nivel de *blocks*. Un **block** es un contenedor de *threads*, que al igual que los *threads*, puede ser de 1, 2 o hasta 3 dimensiones. Su identificador **blockIdx** tambien es una variable tipo uint3 que contiene tres campos de tipo entero sin signo, los cuales determinan la posición del*block* en las 3 dimensiones del *blocks*.

El nivel superior en la jerarquía es el grid. Un grid es el conjunto de todos los blocks que a su vez contienen threads en un lanzamiento de kernel. Al lanzar una función kernel

se creará un blocks, para dimensionar los blocks y los threads, se utilizan las variables tipo dim3 gridDim y blockDim respectivamente (las variables dim 3 son un vector con 3 campos enteros, los campos sin definir por defecto se pondrán en 1) [6] y [7].

Un lanzamiento de kernel se declara:

```

_global__kernel<<< gridDim, blockDim >>>(parámetros);

```

Donde <<< gridDim, blockDim >>> dimensiona todo el conjunto de threads en el blocks. Todos threads tendrán una cópia de los parámetros, con la cual, podrán efectuar cálculos especificados en el cuerpo de la función.

La figura 2.1 muestra de manera gráfica los conceptos establecidos anteriormente. En la cual, se muestra de manera general el dimensionamiento del *blocks* en sus tres dimensiones de direccionamiento para los *blocks* y para *threads*.

Las variables gridDim y blockDim son constantes que pueden ser utilizadas en el kernel por todos los threads. Las variables blockldx y threadldx toman rangos de valores:

```

blockIdx.x = {0, 1, ..., gridDim.x - 1}

blockIdx.y = {0, 1, ..., gridDim.y - 1}

blockIdx.z = {0, 1, ..., gridDim.z - 1}

threadIdx.x = {0, 1, ..., blockDim.x - 1}

threadIdx.y = {0, 1, ..., blockDim.y - 1}

threadIdx.z = {0, 1, ..., blockDim.z - 1}

```

#### 2.1.3. Ejemplo de programa en CUDA: Suma de dos vectores

Para aplicar los conceptos establecidos hasta el momento, se desarrollará un programa ejemplo, el cual tiene como objetivo ejecutar en paralelo la suma de dos arreglos host\_a y host\_b (con 5 elementos cada uno, por simplicidad); guardando el resultado en el arreglo host\_c.

En el desarrollo de este ejemplo seguiremos la secuencia básica de un programa en CUDA descrita anteriormente. El primer paso es generar los datos en el *host*, los cuales se quiere procesar.

```

// Generación de datos en el host:

const int arraySize = 5;

const int host_a[arraySize] = { 1, 2, 3, 4, 5 };

const int host_b[arraySize] = { 10, 20, 30, 40, 50};

int host_c[arraySize] = { 0, 0, 0, 0, 0 };

```

Para hacer uso de la memoria del *device* es necesario reservarla, esto se realiza con la función de CUDA *cudaMalloc*, la cual asigna espacio en la memoria DRAM (Dynamic

Figura 2.1: Dimensionamiento de un grid CUDA, con el lanzamiento de kernel: \_global\_kernel<<< gridDim, blockDim >>> (void);

Random-Access Memory) del device. El segundo parámetro size\*sizeof(int) corresponde al número de bytes a reservar.

```

// Asignación de memoria en el device:

cudaMalloc((void**)&dev_c, size * sizeof(int));

cudaMalloc((void**)&dev_a, size * sizeof(int));

cudaMalloc((void**)&dev_b, size * sizeof(int));

```

Una vez reservado la memoria en el device y generado los datos a procesar, debemos transferir los datos del host hacia el device, esto se realiza mediante la función cuda-Memcpy.

```

// Envío de los datos de entrada hacia el device:

cudaMemcpy(dev_a, host_a, size * sizeof(int), cudaMemcpyHostToDevice);

cudaMemcpy(dev_b, host_b, size * sizeof(int), cudaMemcpyHostToDevice);

```

El programa requiere realizar 5 sumas, como no existe dependencia de datos entre los arreglos de entrada, se pueden realizar en paralelo. Para esto se necesitan 5 threads, los cuales fueron organizados en un bloque que contiene los 5 threads.

```

// Dimensionamiento del grid para la función kernel

dim3 blockDim;

// Dimensionamiento de blocks

gridDim.x = 1; gridDim.y = 1; gridDim.z = 1; // Un bloque

// Dimensionamiento de Threads, 5 hilos en el eje x por bloque

dim3 blockDim;

blockDim.x = size; blockDim.y = 1; blockDim.z = 1;

// Lanzamiento del kernel con un threadspara cada elemento del arreglo

addKernel<<<gridDim, blockDim>>>(dev_c, dev_a, dev_b);

```

El cuerpo del kernel consta de la suma de los arreglos dev\_a y dev\_b, guardando el resultado en el arreglo dev\_c.

```

// Función kernel, ejecutada en el device

__global__ void addKernel(int *c, const int *a, const int *b)

{

int i = threadIdx.x;

c[i] = a[i] + b[i];

}

```

Las variables dimGrid y dimBlock, son las que dimensionan los threads en el blocks. La figura 2.2 muestra de manera más clara como impactan estas variables en el blocks, en la cual, se ilustra el blocks generado por el kernel del programa suma de dos vectores. La variable i que se encuentra en el cuerpo del kernel, se crea en los 5 threads, toma valores diferentes en cada threadsdebido a que threadldx.x varia de cero a 4 (blockDim.x - 1 = 5 - 1). Por lo que i indexará localidades diferentes en los arreglos  $dev_a$ ,  $dev_b$  y  $dev_c$ .

Figura 2.2: Grid generado por el kernel suma de dos vectores

Además, se agregó la función *cudaDeviceSynchronize()* para que el *host* espere a que el *device* termine de ejecutar el *kernel*, para que el arreglo *dev\_c* de salida contenga los elementos calculados por el *kernel*.

```

// Esperar que el kernel termine de ejecutarse totalmente. cudaDeviceSynchronize();

```

En este punto ya se calculó la suma, por lo que es tiempo de transferir los resultados del *device* al *host* y liberar la memoria utilizada en el *device*.

```

// Copia del arreglo procesado hacia el host.

cudaMemcpy(host_c, dev_c, size * sizeof(int), cudaMemcpyDeviceToHost);

//Liberación de la memoria del device

cudaFree(dev_c); cudaFree(dev_a); cudaFree(dev_b);

```

El código completo de este ejemplo se encuentra en el apendice ??. El resultado del programa debe ser  $host_c = \{11, 22, 33, 44, 55\}$ . Este programa se puede utilizar para comprobar la correcta instalación de los drivers del GPU, así como del software de CUDA.

#### 2.1.4. Medición de tiempos de ejecución en el GPU

La medición de tiempos en CUDA se realiza mediante "eventos" Un evento es una estampa de tiempo del GPU que se registra en un punto, en el tiempo, especificado por el usuario. Utiliza un reloj propio del GPU, independiente del reloj del CPU. El tiempo resultante mediante eventos está en el orden de los mili-segundos. Es posible crear más de un evento, además de poder colocar un evento dentro de otro; esto último es útil cuando se requiere medir tiempos parciales [8], [6]. Para indicar la sintaxis del código se utilizará el color azul para diferenciarla del texto común, para mayor detalle revisar CUDA API Reference Manual [9].

La secuencia básica para el manejo de eventos es la siguiente:

- Crear las variables, del tipo cudaEvent, de inicio y paro. cudaEvent\_t start, stop;

- Crear el evento de inicio y paro.

cudaEventCreate( &start ); cudaEventCreate( &stop );

- Guardar la estampa de tiempo inicial. cudaEventRecord( start , 0);

- 4. Escribir la parte de código del *device* que se desea medir. Alguna tarea en el GPU: copias de memoria, ejecución de *kernel*.

- 5. Guardar la estampa de tiempo final. El segundo parámetro corresponde al *stream* en el que se está ejecutando éste código (por defecto se trabaja con el *stream* cero). cudaEventRecord( stop, 0);

- 6. Esperar a que el GPU termine su ejecución hasta la estampa de paro. cudaEventSynchronize( stop );

- Calcular la diferencia entre la estampa final y la inicial. El tiempo se guarda en la variable elapsedTime, en milisegundos. float elapsedTime;

cudaEventElapsedTime(&elapsedTime, start, stop);

Destruir los eventos de inicio y paro. cudaEventDestroy( stop ); cudaEventDestroy( start );

Para visualizar todas las operaciones realizadas durante todo el programa, ver el tiempo y los recursos empleados; *Visual Profiler* de NVIDIA puede ser útil, el cual se proporciona de manera gratuita en el *CUDA Toolkit*. Además, la herramienta de depuración *Nsight* junto con *Visual Studio* o *Eclipse*, también es capaz de realizar un análisis de tiempos. Para más detalles ver el capítulo 3 de [10] y el capítulo 4 de [11].

#### 2.2. Arquitectura GPU

#### 2.2.1. Clasificación de sistemas de cómputo

El sistema de clasificación de Flynn divide a todo el mundo de computo en cuatro grupos: SISD (Single Instruction Single Data), SIMD (Single Instruction Multiple Data), MISD (Multiple Instruction Single Data) y MIMD (Multiple Instruction Multiple Data). El sistema SISD son computadoras von Neumann con un sólo procesador, mientras que los sistemas SIMD son computadoras pipeline.

Las computadoras MIMD trabajan de manera asíncrona. Cada procesador ejecuta su propio programa con un control individual, por lo que multiples *threads* de control son ejecutados simultáneamente. Por otra parte, en las computadoras SIMD, los elementos de procesamiento están hechos de unidades aritméticas y lógicas (ALUs), memoria local y una unidad de comunicación para tener acceso a la red de interconexión. Debido a que un solo decodificador de instrucciones está presente, la ejecución de un programa SIMD es siempre síncrona.

Los arreglos sistólicos son una combinación de los sistemas SIMD MIMD y pipeline. Se maneja por un reloj principal, contiene multiples elementos de procesamiento interconectados. Se alimenta constantemente desde el exterior con datos hacia los procesadores, los cuales mediante su red de conexión pueden pasar resultados entre procesadores [12].

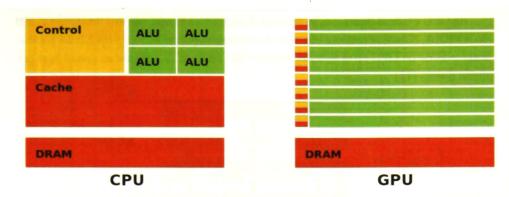

#### 2.2.2. Características de los GPU

Los GPU son especiales para cómputo intensivo, altamente paralelo. Está diseñado para dedicar más transistores para el procesamiento de datos que a la captura de datos en caché y al control de flujo del programa (ver figura 2.3), esto último se debe a que el mismo programa es ejecutado en muchos *threads* en paralelo. Tienen su propia memoria (DRAM), memorias compartidas y registros, las cuales establecen su propia jerarquía de memoria.

Las arquitecturas de los GPUs se agrupan por su compute capability, la cual se representa por "y.x", donde "y" es el número de revisión mayor y "x" es el número de revisión menor (por ejemplo, compute capability 2.1). Devices con el mismo número de revisión mayor tienen la misma arquitectura de núcleos. El número de revisión mayor es 3 para devices basados en la arquitectura Kepler, 2 para devices basados en la arquitectura Fermi, y 1 para devices basados en la arquitectura Tesla. El número de revisión menor corresponde a una mejora de la arquitectura en el incremento de los núcleos, además de la posibilidad de incluir nuevas características. [6]

Figura 2.3: Diferencias CPU y GPU.

#### 2.2.3. Multiprocesadores

La arquitectura GPU de NVIDIA está construida por un arreglo escalable de Streaming Multiprocessors (SMs). Un SM es un arreglo de núcleos llamados Streaming Processor (SP), los cuales realizan las operaciones aritméticas y lógicas de los kernels. Cuando en un programa CUDA, el host realiza un lanzamiento de kernel, los blocks del blocks son enumerados y distribuidos hacia los SMs disponibles para la ejecución del código de los threads. Los threads contenidos por un bloque se ejecutan al mismo tiempo en un multiprocesador. Cuando la ejecución de un bloque termina, nuevos bloques son distribuidos en los multiprocesadores vacantes.

Un SM está diseñado para ejecutar cientos de threads de manera concurrente. Para manejar un gran número de threads, emplea una arquitectura única llamada SIMT (Single-Instruction, Multiple-Thread). En la cual el SM crea, maneja, agenda y ejecuta los threads en grupos de 32 threads paralelos, llamados warps. Los threads que componen el blocks empiezan juntos pero tienen su propio contador de instrucciones y sus registros, lo que les permite ejecutarse independientemente. La arquitectura SIMT habilita a los programadores escribir código paralelo a nivel de thread, los cuales pueden ser independientes o trabajar de manera coordinada [6].

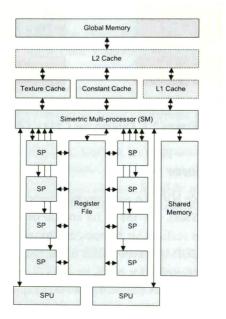

En la figura 2.4, se muestra el diagrama a bloques de un SM, como se puede observar, un SM cuenta con uno o más bloques SPU (Special-Purpose Unit), los cuales realizan instrucciones especiales de alta velocidad, operaciones tales como : seno, coseno y exponenciales. Además, cuenta con un bloque de registros que trabaja a la misma velocidad que los núcleos SP, por lo tanto no tiene tiempo de espera en ésta memoria. También cuenta con un bloque de memoria compartida, la cual es accesible sólo para un SM, puede ser usada como caché manejándola desde el código del kernel.

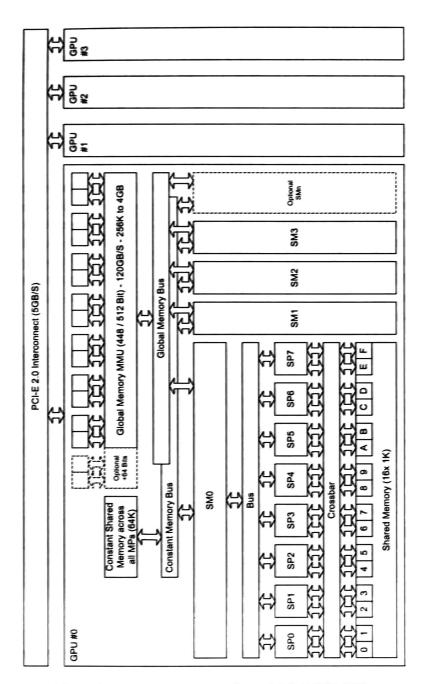

Cada SM tiene un bus separado para los espacios de memoria *texture*, constante y global. La memoria *texture* y constante son de solo lectura y se encuentran sobre la memoria global. La memoria global es suministrada via GDDR (Graphic Double Data Rate) cuyo bus puede ser de hasta 512 bits, dando un ancho de banda de 5 a 10 veces más que el encontrado en CPUs, arriba de 190 GB/s con el hardware Fermi.

En GPU # 0 de la figura 2.5, se muestra el diagrama a bloques de un GPU G80/GT200 de NVIDIA, el cual se conecta con el *host* mediante el puerto PCI express 2.0. Es posible tener más de un GPU en el sistema, mismos que también se comunican con el *host* por dicho puerto [11].

Figura 2.4: Diagrama de un streaming processor (SP)

Figura 2.5: Diagrama a bloques de un GPU (G80/GT200).

#### 2.2.4. Jerarquía de memoria

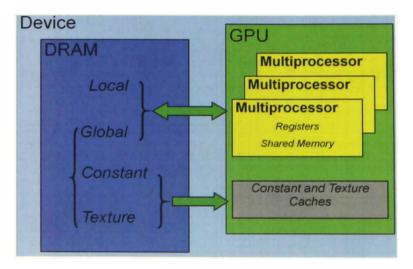

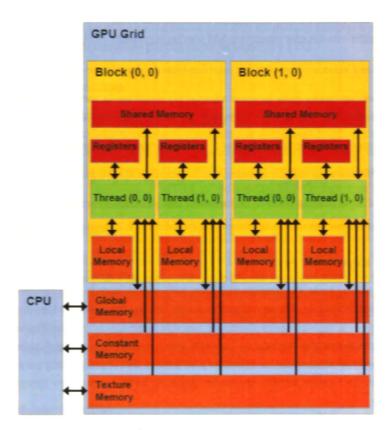

En CUDA, la memoria del host y la del device son entidades separadas. Por lo que es necesario hacer llegar los datos del CPU hacia el GPU, para que sean procesador por el GPU y posteriormente entregar los resultados hacia el CPU. El device cuenta con una memoria DRAM, en la cual, como se muestra en la figura 2.6, se encuentran las memorias: global, local, constante (constant) y texture. En el GPU se encuentran los SM, los cuales tienen su propia memoria compartida (shared) y registros, además de memorias cache para el manejo de las memorias constante y texture.

La jerarquía de memoria se establece al observar el ámbito de las variables en los diferentes tipos de memoria, además de observar quien puede escribir y leer en ellas. Para visualizar esto, nos basaremos en la figura 2.7, en la cual con flechas con una dirección se indica que son de solo lectura, mientras que con una flecha bidireccional se indica que puede ser de lectura y escritura. Como vemos, el CPU solo puede leer y escribir en la memoria DRAM (global, constant y texture). Los threads pueden leer de la memoria compartida propia del block que lo contiene, tienen su propio bloque de registros y memoria local; además, tienen acceso a la DRAM.

Figura 2.6: Localización de memorias del device

La tabla 2.2 muestra como diferenciar y declarar las variables en los diferentes espacios de memoria; así como el ámbito y el tiempo de vida que tendrán. Por ejemplo utilizando el calificador de variable \_\_constant\_\_, se reservará espacio en la memoria constante, la cual se encuentra en la DRAM, todos los threads de todos los bloques podrán leer de ella, mientras no se libere dicha memoria seguirá reservada en el device durante toda la aplicación. Entendemos como aplicación a la ejecución de todo el código host y todo el código device, pudiéndose realizar más de un lanzamiento de kernel durante su tiempo de ejecución.

| Declaración de variable             | Memoria que utiliza | Ámbito | Tiempo de vida |

|-------------------------------------|---------------------|--------|----------------|

| Variables diferentes a los arreglos | Registro            | Thread | Kernel         |

| Arregios                            | Local               | Thread | Kernel         |

| _shared_                            | Compartida          | Block  | Kernel         |

| _device_                            | Global              | Grid   | Aplicación     |

| constant                            | Constante           | Grid   | Aplicación     |

Tabla 2.2: Identificadores de variables.

Figura 2.7: Ámbito de las memorias del device

El ancho de banda y la latencia son dos conceptos importantes para describir las características de las memorias. Ancho de banda, es la cantidad de datos que se pueden leer o almacenar en la DRAM en un periodo dado de tiempo. Latencia, es el tiempo que toma en realizar la petición de búsqueda (fetch request) de alguna localidad de memoria [11]. A continuación se presentarán los diferentes tipos de memorias que se encuentran en el device, puntualizando sus características más representativas.

#### 2.2.4.1. Memorias Caché

Una caché es un banco de memoria de alta velocidad que se encuentra físicamente cercano al núcleo de procesamiento. Son caras en términos de silicio, lo cual se traduce en grandes chips, baja producción y procesadores más caros. La máxima velocidad de una caché es inversamente proporcional al tamaño de la caché. La caché L1 es la más rápida, pero está limitada en tamaño generalmente alrededor de 16K, 32K o 64K. Por lo general es asignada a un solo procesador. La caché L2 es más lenta, pero más larga, típicamente de 256K a 512K.

La arquitectura *Fermi* fue la primera implementación GPU, en incorporar una caché L1 por SM y una caché L2 que comparten todos los SM [11].

Las caché con las que cuenta un SM son las siguientes [13]:

- Shared memory para rápidos intercambios de datos entre threads.

- Constant cache para lecturas rápidas de datos en la memoria constante, con la capacidad de que un dato se lea por los threads que lo soliciten.

- Texture cache para incrementar el ancho de banda de la memoria global.

- L1 Cache para reducir la latencia a la memoria local o global.

- L2 Cache acelera accesos de memoria con patrones irregulares.

Para mayor detalle de las memorias caché L1 y L2, revisar el capítulo 5 de [10].

#### 2.2.4.2. Registros

Cada thread tiene sus propios registros, esta memoria es la más rápida de todas por su localidad, debido a que se encuentra en los multiprocesadores. Una función kernel típicamente usa registros para mantener variables que son accesadas frecuentemente y son privadas para cada thread. Las variables (no arreglos) que son declaradas en el cuerpo del kernel se almacenan en registros y se genera una copia privada para cada thread que ejecuta la función kernel, las cuales dejan de existir cuando su thread termina su ejecución.

#### 2.2.4.3. Memoria local

Accesos de memoria local ocurren solo para variables automáticas. Una variable automática es aquella que se declara en el *código device* sin ninguno de los calificadores \_\_device\_\_, \_\_shared\_\_, o \_\_constant\_\_ . Generalmente, las variables automáticas residen en registros, excepto los casos siguientes:

Arreglos que podrían consumir demasiado espacio en la memoria de registros.

Cualquier variable que el compilador decide pasar a la memoria local, cuando el kernel utiliza más registros que los disponibles por SM.

#### 2.2.4.4. Memoria compartida

La memoria compartida (shared) es una caché L1 controlada por el usuario. Se crea una versión privada por cadablock, cada thread en el block puede tener acceso a dicha memoria durante la ejecución del kernel, mientras que, thread de otros blocks no pueden hacerlo. Una vez que el kernel termina su ejecución, el contenido de las varibles shared dejan de existir.

Los accesos a la memoria compartida es sumamente rápido y altamente en paralelo. Los programadores de CUDA a menudo usan memoria compartida para mantener una porción de los datos de la memoria global que es altamente usada en la fase de ejecución del *kernel*. Además de que es un medio eficaz para que los *threads* cooperen al compartir los datos de entrada y el resultado parcial de su trabajo [5] y [11].

#### 2.2.4.5. Memoria constante

Memoria de solo lectura para el *device* que es escrita por el *host*. Se utiliza para almacenar datos que no cambiarán en el transcurso de la ejecución del *kernel*. Las variables *constant* se almacenan en la memoria global pero utilizan la caché *constant* para su acceso eficiente. Con patrones apropiados de acceso, se pueden conseguir accesos rápidos y en paralelo. El hardware NVIDIA proporciona 64KB de ésta memoria.

#### 2.2.4.6. Memoria Global

El host puede transferir datos de ella, es el tipo de memoria de mayor capacidad. Los accesos a la memoria global son lentos, sin embargo, las variables globales son visibles para todos los threads de todos los kernels. Su contenido se mantiene durante toda la aplicación. Por lo tanto, variables globales se pueden utilizar como un medio para que los threads colaboren (compartan datos) a través de los bloques. Las variables globales se utilizan frecuentemente para pasar información de un lanzamiento de kernel a otro [5].

#### 2.2.4.7. Memoria Texture

Está montada sobre la memoria global, con mecanismos internos para su acceso en una, dos o hasta tres dimensiones. Es memoria de solo lectura para el *device*, es escrita por el *host*. Para el manejo de la memoria utiliza arreglos CUDA (*cuda array*), los cuales tienen características para su manejo en 2 y 3 dimensiones, solo pueden ser leídos por los *kernel* a travez de funciones *texture* y debe ser ligado a una referencia *texture*.

A continuación se presentará la secuencia básica para el manejo de Texture en 3 dimensiones. En azul se presenta fracciones del código ejemplo del apéndice A.2. En el cual se lee un arreglo de 3 dimensiones, se le suma uno y el resultado se copia en un arreglo lineal. Con esto se puede observar el manejo de un arreglo de 3 dimensiones y como guardarlo en un arreglo lineal.

1. Declaración de las referencias *texture* de 3 dimensiones, esto se debe realizar fuera de la función principal.

texture<float, cudaTextureType3D, cudaReadModeElementType> textReference;

2. Asignación de memoria en el device mediante CUDA arrays, estableciendo el tipo de dato del arreglo mediante cudaCreateChannelDesc.

cudaChannelFormatDesc channelDesc;

channelDesc = cudaCreateChannelDesc<float>();

- Declaración de los CUDA array. cudaArray \*cudaArray

- Dimensionamiento del CUDA array, estableciendo su volumen. volumeSize = make\_cudaExtent(size, size, size); cudaMalloc3DArray(&cudaArray, &channel, volumeSize);

- 5. Preparación de los parámetros de copia en tres dimensiones. Estableciendo el tipo y tamaño de la copia. *make\_cudaPitchedPtr* cambia el arreglo lineal *host\_CubeMatrix* en un arreglo tridimensional.

copyparms.extent = volumeSize; copyparms.dstArray = cudaArray; // Arreglo destino. copyparms.kind = cudaMemcpyHostToDevice; copyparms.srcPtr = make\_cudaPitchedPtr((void\*)host\_CubeMatrix, ... sizeof(float)\*size, size, size); // Arreglo fuente.

- Envió de los datos hacia el device. cudaMemcpy3D(&copyparms);

- 7. Ligar el *CUDA array* con la referencia *texture*. cudaBindTextureToArray(textReference, cudaArray, channel);

- 8. Ejecutar la función *kernel*. kernel<<< dimGrid, dimBlock >>>( *device\_*CubeMatrix, size );

- Copiar el arreglo procesado cuOutputArray hacia el host. cudaMemcpy(host\_CubeMatrix, device\_CubeMatrix, ... sizeof(float)\*size\*size\*size, cudaMemcpyDeviceToHost);

- 10. Desenlazar la referencia *texture* para liberar el recurso. cudaUnbindTexture(textReference);

- 11. Liberar los *CUDA array* del *device*. cudaFreeArray(cudaArray);

#### 2.2.4.8. Memoria Surface

La memoria surface es similar a texture, con la diferencia que tiene funciones de lectura y de escritura. En azul se presenta fracciones del código ejemplo del apéndice A.3. En el cual se lee un arreglo de 2 dimensiones, se le suma uno y el resultado se copia en un arreglo de 2 dimensiones. Con esto se puede observar el manejo de un arreglo de 2 dimensiones, esto es útil cuando se requiere procesar algoritmos que utilicen arreglos matriciales.

La secuencia básica para el manejo de Surface en 2 dimensiones es la siguiente.

1. Declaración de las referencias *surface* de 2 dimensiones, esto se debe realizar fuera de la función principal.

```

surface<void, cudaSurfaceType2D> inputSurfRef;

surface<void, cudaSurfaceType2D> outputSurfRef;

```

Asignación de memoria en el device mediante CUDA arrays, estableciendo el tipo de dato del arreglo mediante cudaCreateChannelDesc.

```

cudaChannelFormatDesc channelDesc;

channelDesc = cudaCreateChannelDesc<float>();

```

- Declaración de los CUDA array. cudaArray\* cuInputArray; cudaArray\* cuOutputArray;

- Dimensionamiento del CUDA array, estableciendo su volumen. cudaMallocArray(&cuInputArray, &channelDesc, ... width, height, cudaArraySurfaceLoadStore); cudaMallocArray(&cuOutputArray, &channelDesc, ... width, height, cudaArraySurfaceLoadStore);

- Envió de los datos hacia el device. cudaMemcpyToArray(cuInputArray, 0, 0, h\_data, size, ... cudaMemcpyHostToDevice);

- Ligar el CUDA array con la referencias surface.

cudaBindSurfaceToArray(inputSurfRef, cuInputArray);

cudaBindSurfaceToArray(outputSurfRef, cuOutputArray);

- Ejecutar la función kernel.

copyKernel

dimGrid, dimBlock >>>( width, height );

- Copiar el arreglo procesado cuOutputArray hacia el host. cudaMemcpyFromArray(h\_data\_out, cuOutputArray, 0, 0, size, ... cudaMemcpyDeviceToHost);

Liberar los CUDA array del device. cudaFreeArray(cuInputArray); cudaFreeArray(cuOutputArray);

#### 2.3. Buenas prácticas de programación

#### 2.3.1. Utilización de los multiprocesadores

Una de las claves para buen desempeño es mantener ocupados los multiprocesadores en el device lo más posible. Es importante diseñar la aplicación para que utilicen los blocks y threads de tal manera que maximice la utilización de los recursos de hardware del device (multiprocesadores, memoria compartida y registros). Las instrucciones en los threads se ejecutan secuencialmente, y como resultado, ejecutar otros warps cuando un warp está en pausa es la única manera de ocultar las latencias y mantener el hardware ocupado.

Es importante una métrica para la determinación de cuan efectivamente el hardware se mantiene ocupado. Esta métrica es *occupancy*. **Occupancy** es la razón del número de *warps* activas por multiprocesador (*warps1*) y el número máximo de las *warps* activas posibles (*warps2*). (El último número está determinado por el hardware del GPU que se esté usando). Otra manera de ver *occupancy* es el porcentaje de la capacidad del hardware para procesar *warps* que están activamente en uso [8].

$$occupancy = \frac{warps1}{warps2}$$

NVIDIA proporciona una herramienta en excel que calcula la occupancy, el cual facilita a los desarrolladores afinar el optimo balance de recursos del GPU y para probar diferentes escenarios más facilmente. Esta herramienta llamada "CUDA Occupancy Calculator" se encuentra en el subdirectorio tools de CUDA Toolkit installation. Los recursos que impactan sobre occupancy son el dimensionamiento de blocks y threads, los registros en los threads y la memoria compartida por los blocks. Para ilustrar como impactan estos recursos en la occupancy, se utilizará la herramienta antes mencionada.

Las características y las especificaciones técnicas del device se presentan de manera detallada en el apéndice F.1 de "NVIDIA CUDA C Programming Guide" [6] y están agrupadas según su compute capability. A continuación se presentará un ejemplo para el cálculo de la occupancy, para esto, tomaremos como base un device de compute capability 2.0, cuyas características son las siguientes:

- Número máximo de threads por multiprocesador es 1536.

- Número de threads por blocks es 32.

- Número máximo de warps activas por multiprocesador es 48.

- Número máximo de blocks por multiprocesador es 8.

- Número máximo de threads en un block es 1024.

- Numero máximo de registros de 32 bits por multiprocesador es 32000.

- La cantidad máxima de memoria compartida por multiprocesador es 49182 bytes.

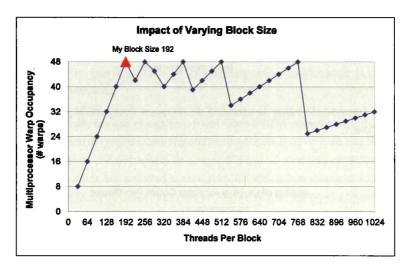

Para tener una occupancy del 100 %, se deben de activar las 48 warps, lo cual implica que se utilizarán los 1536 threads disponibles por multiprocesador. Para que esto pase, el producto del número de blocks por multiprocesador y el número de threads por block debe ser 1536. Si elegimos utilizar los 8 bloques por multiprocesador, a cada block le corresponderá 192 threads, mientras que, si elegimos tener solo un block, máximo se podrá utilizan los 1024 threads. Esto último acarreará tener una occupancy del 67 %, debido a que con los 1024 threads se utilizarán solo 32 warps de las 48 disponibles por multiprocesador (32 warps utilizadas / 48 warps disponibles \* 100 = 67 %). La figura 2.8 muestra el impacto de variar el número de threads por block en la activación de las warps. Para una occupancy del 100 % se debe elegir el número de threads por block de manera que se utilicen las 48 warps disponibles.

Figura 2.8: Impacto de variar el tamaño de los blocks en la occupancy.

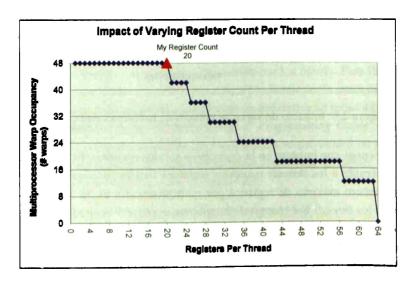

Otro recurso que impacta en la occupancy son los registros. El almadenamiento en registros permite a los threads mantener variables locales cercanas para su rápido acceso. El número máximo de registros por multiprocesador es de 32000, los cuales se reparten en los threads que maneje dicho multiprocesador. Por ejemplo, si se utilizan los 1536 threads, entonces le corresponden 20 registros máximo por thread, para tener una occupancy del 100 %. La figura 2.10 muestra el impacto de variar el número de registros en la utilización de las warps. Entre más se sobrepase el límite de 20 registros, menos warps podrán utilizarse para el computo del kernel, lo cual impactará notablemente en la occupancy.

La memoria compartida también puede ser una restricción en la occupancy. El volumen total de memoria compartida (shared) se reparte en el número de blocks que se hayan creado por multiprocesador. En nuestro ejemplo, se tiene con 49152 bytes y se estableció que se utilizarían 192 threads por block, lo cual permite tener hasta 8 blocks en el multiprocesador, por consiguiente, le corresponde hasta 6144 bytes a cada block. En la figura 2.9 se muestra como afecta el sobrepasar el límite de 6144 bytes para una occupancy del 100 %.

Figura 2.9: Impacto de variar la cantidad de memoria compartida por *block* (en bytes) en la *occupancy*.

Figura 2.10: Impacto de variar el número de registros por thread en la occupancy.

# 2.3.2. Concurrencia host/device

Además de la concurrencia a nivel de *threads*, CUDA también cuenta con algunas herramientas de hardware y software que permiten realizar operaciones al mismo tiempo en el *host* y en el *device*. Dichas operaciones son las siguientes:

- Concurrencia CPU/GPU: Debido a que el CPU y el GPU son dispositivos separados, pueden operar independiente el uno del otro. Las funciones kernel se pueden ejecutar a la par de alguna función en el host, si se desea que el host espere a que el device termine de ejecutar alguna función se puede utilizar la barrera de sincronía cudaDeviceSynchronize(). El programa debe ser particionado de manera que el código con poco o níngún paralelismo de datos, se ejecute en el host, mientras que el código con alto paralelismo de datos se ejecute en el device.

- Concurrencia Memcpy/kernel: Algunos GPUs tienen la capacidad de tener más

de un mecanismo de copia, por lo que las transferencias de datos entre el host y

el device pueden ser realizadas mientras los SMs están procesando kernels. Para

verificar esto, se requiere verificar la propiedad del device llamada asyncEngineCount, la cual es 1 para devices que lo soportan.

- Concurrencia Multi-GPU: Es posible conectar varios GPU mediante el puerto PCI-express, con los cuales se incrementa considerablemente la capacidad de computo en paralelo.

Para mayor detalle revisar el capítulo 6 del libro CUDA Handbook [13].

Para ejecutar ciertas operaciones simultáneamente en el device, se requiere el uso de streams. Un stream es una secuencia de comandos que se ejecutan en orden. Diferentes streams pueden ejecutar sus comandos en cualquier orden con respecto a otro stream o de manera concurrente. Por defecto el código device se ejecuta en el stream cero, por lo tanto, si no se especifica el parámetro correspondiente al stream en un lanzamiento de kernel o en una transferencia de memoria, se trabajará dentro del stream cero.

Al igual que los eventos, los streams se pueden sincronizar. Con cudaDeviceSynchronize, el device espera a que todos los comandos predecesores en todos los streams han terminado. CudaStreamSynchronize toma como parámetro un determinado stream y espera a que todos los comandos predecesores a dicho stream terminen. Con cudaStreamWaitEvent(), un determinado stream espera a que un evento, dado como parámetro, termine antes de continuar con su ejecución de comandos. Para verificar que un stream ha terminado su ejecución, se emplea la instrucción cudaStreamQuery() [6].

## 2.3.3. Optimizaciones de memoria

Las optimizaciones de memoria son de vital importancia para mejorar rendimiento. Su objetivo es el de maximizar el uso del hardware para obtener el mayor el ancho de banda posible durante las transferencias de datos.

- Es importante minimizar las transferencias de datos entre el host y el device, incluso si eso significa ejecutar más kernels en el GPU que no demuestran aceleración comparándolo con ejecutarlo en el CPU.

- Largas transferencias de memoria tiene mejor rendimiento que realizar numerosas transferencias pequeñas, esto debido al encabezado asociado a cada transferencia.

- Para incrementar la utilización del device y reducir tiempos, es recomendable realizar las transferencias de memoria mientras se está ejecutando funciones kernel.

- Es recomendable utilizar memoria compartida para evitar transferencias redundantes de la memoria global. La secuencia típica del manejo de esta memoria es la siguiente:

- Cargar los datos de la memoria global a la memoria compartida.

- Sincronizar todos los threads del block para que cada threads pueda leer el dato correcto que pudo ser cargado por algún otro thread del block.

- Procesar los datos de la memoria compartida.

- Sincronizar de nuevo, si es necesario, para asegurar que la memoria compartida ha sido actualizada con los resultados.

- Escribir el resultado en la memoria global. Si ya no se requiere mantener dichos datos en el device, se procede a transferir los resultados de la memoria global al host [6].

- La caché texture está optimizada con localidad espacial en dos dimensiones, por lo tanto, threads del mismo blocks que leen direcciones texture o surface que se encuentran cercanas tendrán mejor desempeño. Leer la memoria del device a través de una referencia texture o surface puede ser una alternativa ventajosa para leer memoria global, los beneficios son los siguientes:

- Mayor ancho de banda se puede obtener si los accesos corresponden a localidades de memoria cercanas, aun cuando las lecturas no siguen los patrones de acceso que se deben respetar para buen desempeño (ver las secciones 5.3.2.1 y 5.3.2.4 de CUDA Programming Guide [6]).

- Cálculos para el direccionamiento de la memoria se realizan fuera del kernel por unidades dedicadas.

- Datos de entrada de 8 y 16 bit pueden ser convertidos opcionalmente a valores de punto flotante de 32 bits en el rango de [0.0, 1.0] o [-1.0, 1.0] [6].

- Asignar y liberar memoria del device mediante cudaMalloc() y cudaFree() son operaciones costosas, por lo tanto, se debe buscar reutilizar la memoria del device lo más posible para reducir su impacto en el desempleño total de la aplicación [8].

# 2.4. Resumen del capítulo

El capítulo presenta una base introductoria a los GPU y a la programación en CUDA C. En donde el GPU trabaja en conjunto con el CPU, los cuales se comunican mediante el puerto *PCI express*. El lenguaje de programación que se utiliza es CUDA C, el cual está basado en el lenguaje tradicional C, al cual se le agregaron funciones especiales para el manejo de la memoria y de los procesadores del GPU. Se presenta una secuencia básica de un programa en CUDA, además de un ejemplo completo, el cual puede ser utilizado para comprobar la correcta instalación de los controladores del GPU.

Uno de los temas cruciales en la programación en CUDA es el manejo y dimensionamiento de los threads para maximizar la utilización de los SM, por lo cual se dedica una sección en donde se presenta como dimensionar todo el conjunto de threads para el procesamiento paralelo de datos.

El correcto manejo de la memoria es vital para obtener buenos resultados en los cálculos y para reducir tiempos de ejecución. Una sección se dedica al manejo de la memoria, en donde se muestran las características de los diferentes tipos de memoria y como transferir datos entre el CPU y el GPU. CUDA C tiene funciones especiales para manejar la memoria DRAM del GPU en 2 y 3 dimensiones mediante texture y surface, se presenta la secuencia básica para utilizar texture en 3 dimensiones y otra secuencia para manejar surface de 2 dimensiones.

Al final del capítulo se presenta una sección en donde se puntualizan buenas prácticas de programación en CUDA, como la utilización de los multiprocesadores, la concurrencia entre el CPU y el GPU, y el manejo de memoria.

# Capítulo 3

# Transformación de algoritmos con bucles anidados

# 3.1. Antecedentes matemáticos

# 3.1.1. Vectores y matrices

Los vectores enteros en  $\mathbb{Z}^n$  poseen n elementos, se manejarán por defecto como vectores fila con elementos enteros, por ejemplo  $\mathbf{i} = (1, 2, \dots, n)$ . El vector nulo,  $\mathbf{0}$ , tiene todos sus n elementos igual a cero.

A continuación enumeraremos algunas relaciones de orden entre los vectores **a** y **b** de *n* elementos:

- **a** y b son iguales, escrito a = b, si  $a_i = b_i$ ,  $1 \le i \le n$ .

- **a** es menor que **b**, escrito **a** < **b**, si  $a_i < b_i$ ,  $1 \le i \le n$ .

- $\mathbf{a} \leq \mathbf{b}$ , si  $a_i \leq b_i$ ,  $1 \leq i \leq n$ , que no es lo mismo que  $\mathbf{a} < \mathbf{b} \vee \mathbf{a} = \mathbf{b}$ .

- a es lexicográficamente menor que b, escrito a < b, si existe un j,  $1 \le j \le n$ , tal que a < j b.

- **a** es lexicográficamente menor que **b** a nivel j, escrito **a**  $<_j$  **b**, si  $a_i = b_i$ ,  $1 \le i < j \le n$  y  $a_j < b_j$ .

- $a \leq b$ , si  $a < b \vee a = b$ .

Un vector lexicográficamente positivo es un vector cuyo primer elemento (de izquierda a derecha) diferente de cero, es positivo, por ejemplo (0, 2, -11, 0). De manera similar, un vector lexicográficamente negativo es un vector cuyo primer elemento (de izquierda a derecha) diferente de cero, es negativo, por ejemplo (0, -2, 11, 0).

El vector signo es el signo de sus elementos. Por lo tanto, si  $\mathbf{d} = (2,-3,0)$ , entonces  $\operatorname{sig}(\mathbf{d}) = (sig(2), sig(-3), sig(0)) = (1,-1,0)$ .

Una matriz real A de  $n \times m$  tiene n filas y m columnas de números de números reales

$$\mathbf{A}^{m \times n} = \begin{pmatrix} a_{11} & a_{12} & \cdots & a_{1m} \\ a_{21} & a_{22} & \cdots & a_{2m} \\ \vdots & \vdots & \vdots & \vdots \\ a_{n1} & a_{n2} & \cdots & a_{nm} \end{pmatrix}$$

El vector  $\mathbf{a}_t$  contiene los elementos de la fila t de la matriz  $\mathbf{A}^{mxn}$ , por ejemplo,  $\mathbf{a}_2 = (a_{21}, a_{22}, \dots, a_{2m})$ . El vector  $\mathbf{a}^r$  contiene los elementos de la columna r de la matriz  $\mathbf{A}^{mxn}$ , por ejemplo,  $\mathbf{a}^1 = (a_{11}, a_{21}, \dots, a_{n1})$ .

# 3.1.2. Reducción de matrices a la forma escalonada

Reducir una matriz de  $m \times n$  a la forma escalonada (echelon form) significa encontrar una matriz unimodular U de  $m \times n$  y una matriz escalonada S, tal que UA = S. Esta reducción siempre es posible; las matrices U y S no son únicas. A continuación se proporciona un método para encontrar tales matrices.

# Algoritmo 3.1 Reducción escalonada de una matriz

```

Entrada: Matriz A entera de m \times n.

Salida: Matriz unimodular U y la matriz escalonada S de m \times n, tal que UA = S

\mathbf{U} \leftarrow I_m, \mathbf{S} \leftarrow \mathbf{A}, i_0 \leftarrow 0

for j = 1, n, 1 do

if existe al menos un elemento s_{ij} no cero con i_0 < i \le m then

i_0 \leftarrow i_0 + 1

for i = m, i_0 + 1, -1 do

while s_{ij} \neq 0 do

\sigma \leftarrow sign(s_{(i-1)j} * s_{ij})

\tau \leftarrow \lfloor |s_{(i-1)j}|/|s_{ij}| \rfloor

Multiplicar \sigma \tau por la fila i y restarlo de la fila (i-1) en (U; S)

Intercambiar las filas i \in (i-1) en (U; S)

end while

end for

end if

end for

```

En algunas aplicaciones, para una matriz A dada, se necesita encontrar una matriz unimodular V y una matriz escalonada S, tal que A = VS. V podría ser la inversa de la matriz unimodular U del algoritmo 3.1. Sin embargo, si U no se necesita, el algoritmo 3.1 puede ser modificado para producir directamente a V y S tal que A = VS. [14]

# Algoritmo 3.2 Reducción escalonada de una matriz (modificada)

```

Entrada: Matriz A entera de m x n.

Salida: Matriz unimodular V y la matriz escalonada S de m \times n, tal que A = VS

\mathbf{V} \leftarrow \mathbf{I}_m, \mathbf{S} \leftarrow \mathbf{A}, i_0 \leftarrow 0

for j = 1, n, 1 do

if existe al menos un elemento s_{ij} no cero con i_0 < i \le m then

i_0 \leftarrow i_0 + 1

for i = m, i_0 + 1, -1 do

while s_{ij} \neq 0 do

\sigma \leftarrow sign(s_{(i-1)j} * s_{ij})

\tau \leftarrow \lfloor |s_{(i-1)j}|/|s_{ij}| \rfloor

Multiplicar \sigma\tau por la fila i y restarlo de la fila (i-1) en S

Multiplicar \sigma \tau por la columna i-1 y sumarlo a la columna i en V

Intercambiar las filas i \in (i-1) en S

Intercambiar las columnas i \in (i-1) en V

end while

end for

end if

end for

```

# 3.1.3. Solución de sistemas de desigualdades lineales

Una desigualdad lineal con n incógnitas puede expresarse:

$$a_1 x_1 + a_2 x_2 + \dots + a_n x_n \le c \tag{3.1}$$

donde  $a_1, a_2, \dots, a_n$  son escalares. De manera similar, un sistema de ecuaciones de desigualdades puede expresarse en su forma matricial:

$$\mathbf{A}\mathbf{x} \le \mathbf{c} \tag{3.2}$$

El problema es encontrar el vector x tal que la desigualdad 3.2 se cumpla. En el capítulo 2 de la tesis [4] se aborda este tema y se presenta el algoritmo de eliminación de Fourier - Motzkin, además de dos métodos de simplificación de sistemas de desigualdades: algoritmo de simplificación Ad - Hoc y el algoritmo de simplificación Exacta.

# 3.2. Modelado de bucles anidados

Un bucle anidado o un nido de bucles es un conjunto de bucles en el que un bucle contiene uno o más bucles del tipo for. Un nido de bucles perfecto es un bucle anidado en el que no existen sentencias entre un bucle y otro, es decir, todas las sentencias se encuentran dentro del bucle más interno. Escribiremos  $L = (L_1, L_2, \dots, L_m)$  para representar en forma vectorial el nido de m bucles. Cada bucle tiene una variable índice

asociada, que en conjunto forman el vector de iteración  $\mathbf{x} = (x_1, x_2, \dots, x_m)$ . Los límites inferiores y superiores de una variable índice  $x_r$ , correspondiente al bucle  $L_r$ , son  $p_r$  y  $q_r$ , respectivamente, donde  $1 \le r \le m$ . Los pasos de las variables índice son unitarios. El cuerpo del nido de bucles es  $H(x_1, x_1, \dots, x_m)$  o  $H(\mathbf{x})$ , el cual es una secuencia de sentencias de asignación. A continuación se presenta de manera general un nido con m de bucles L:

Un espacio de iteración se asocia a un nido de bucles L, el cual contiene un punto, en el espacio m dimensional, por cada iteración. Dicho **punto de iteración** se representa por  $\mathbf{i} = (i_1, i_2, \dots, i_m)$ , donde las valores  $i_1, i_2, \dots, i_m$  corresponden a los valores que toman  $x_1, x_2, \dots, x_m$ , respectivamente, por ejemplo:  $\mathbf{i} = (p_1, q_2, \dots, p_m)$ .

El espacio de iteración se puede representar mediante el conjunto de dos desigualdades llamadas las *restricciones* en x:

Donde los vectores  $\mathbf{p}$  y  $\mathbf{q}$  (con m elementos) son respectivamente los vectores de límite inferior y superior;  $\mathbf{P}$  y  $\mathbf{Q}$  son las matrices de m x m de límite inferior y superior. La ecuación 3.3 se puede escribir ahora como un politopo. Un **politopo** en  $\mathbb{R}^m$  es un conjunto acotado de la forma  $\{\mathbf{x} \in \mathbb{R}^m : \mathbf{x} \mathbf{A} \leq \mathbf{c}\}$  para alguna matriz real  $\mathbf{A}$  y un vector real  $\mathbf{c}$ . Para modelar el espacio de iteración para nuestro nido de bucles original, se escribirá en forma de politopo y se llamará **politopo fuente**. El politopo fuente se representará como  $\mathbf{x} \mathbf{A} \leq \mathbf{b}$ , donde  $\mathbf{A}$  se compone de la concatenación de filas de las matrices  $\mathbf{Q}_0 = -1 * \mathbf{Q}$  y  $\mathbf{P}$ ; de manera similar  $\mathbf{b}$  se compone de la concatenación de filas los vectores  $\mathbf{p}_0 = -1 * \mathbf{p}$  y  $\mathbf{q}$ . [15]

# 3.3. Dependencia de datos

La dependencia de los datos en un nido de bucles es lo que restringe las iteraciones que se pueder ejecutar en paralelo. De allí la importancia de hacer un correcto análisis de dependencia entre las iteraciones en bucles. Una iteración H(j) depende de una iteración diferente H(i), si las siguientes condiciones se cumplen:

- 1. H(i) es ejecutada antes que H(j) en L. esto es, i < j.

- Existe una localidad de memoria a la que se le hace una referencia (de lectura o escritura) por ambas iteraciones, y al menos una de las dos referencias es de escritura.

- 3. Que una localidad de memoria no es escrita por ninguna iteración  $H(\mathbf{k})$  que viene entre  $H(\mathbf{i})$  y  $H(\mathbf{j})$ , tal que  $\mathbf{i} < \mathbf{k} < \mathbf{j}$ .

Los tipos de dependencia de datos son los siguientes:

- De flujo: ocurre cuando una variable es asignada o definida en una sentencia y es usada en una sentencia posterior. También se le conoce como read after write o dependencia verdadera.

- Anti-dependencia: ocurre cuando una variable es usada en una sentencia y es reasignada por una sentencia posterior. También se le conoce como write after read.

- De salida: ocurre cuando una variable es asignada en una sentencia y se modifica su valor en una sentencia posterior.

- De entrada: ocurre cuando una variable es usada por una sentencia y posteriormente se vuelve a utilizar en otra sentencia.

Las dependencias de salida y anti-dependencia surgen por el reuso o reasignación de variables, también son llamadas dependencias falsas. La dependencia de flujo es llamada dependencia verdadera ya que es inherente en el cálculo y no puede ser eliminada por el uso de variables temporales. [16]

Si una iteración H(j) depende de una iteración H(i), entonces la diferencia  $\mathbf{d} = \mathbf{j} - \mathbf{i}$  entres dos puntos de iteración se le llama vector distancia para el nido de bucles L. Ya que por definición  $\mathbf{i} < \mathbf{j}$ , tenemos  $\mathbf{d} < \mathbf{0}$ , esto es, un vector distancia es siempre positivo (lexicográficamente).

N es el número de los distintos vectores distancia de L, y D es el conjunto de estos vectores. La matriz distancia para L es una matriz de N x m cuyas filas se componen de los vectores en D, en cualquier orden. La matriz distancia también se le conoce como matriz de dependencia y se denota por  $\mathcal{D}$ .

Si  $d_{\ell}$  es el primer elemento no cero de un vector  $\mathbf{d} = (d_1, d_2, \dots, d_m)$  a partir de la izquierda, entonces es el elemento líder de  $\mathbf{d}$  y  $\ell$  es el nivel de  $\mathbf{d}$ . El nivel de un vector positivo  $\mathbf{d}$  es  $\ell$  si y solo si  $\mathbf{d} <_{\ell} \mathbf{0}$ . Un nivel de dependencia para  $\mathbf{L}$  es el nivel del vector distancia para  $\mathbf{L}$ . Si  $\ell$  es un nivel de dependencia, entonces decimos que existe

una dependencia en L a nivel  $\ell$ , o que el bucle  $L_{\ell}$  lleva la dependencia. Existen m niveles de dependencia posibles:  $1, 2, \dots, m$ .

El grafo de dependencia de L es un grafo dirigido cuyos vértices son los puntos de iteración de L; y existe una arista dirigida desde un vértice u hacia un vértice v si, y solo si, la iteración correspondiente a v depende de la iteración correspondiente a u. Para dibujar el grafo de dependencia, colocamos todos los puntos del espacio de iteración en un plano m-dimensional (m es el número de bucles anidados) y después, dibujamos una flecha desde el punto de iteración i hacia el punto de iteración j cuando la iteración h(j) dependa de la iteración h(i).

# 3.4. Transformaciones unimodulares

# 3.4.1. Matrices unimodulares

Una matriz unimodular tiene tres propiedades importantes. Primero, es cuadrada, lo cual significa que mapea un espacio de iteración n-dimensional a un espacio de iteración n-dimensional. Segundo, tiene todos sus componentes enteros, por lo que mapea vectores enteros a vectores enteros. Tercero, el valor absoluto de su determinante es uno, por lo que el volumen del espacio de iteración se conserva. Debido a estas propiedades, el producto de dos matrices unimodulares es unimodular y su inversa también es unimodular.

Una transformación compuesta puede ser sintetizada a partir del producto de una secuencia de transformaciones elementales. [16][17]

# 3.4.2. Legalidad de una transformación unimodular

Decimos que una transformación es legal si el programa transformado mantiene las relaciones de dependencia, el programa transformado debe de arrojar el mismo resultado que el programa original. El objetivo de la transformación es cambiar el orden de ejecución del programa manteniendo la dependencia de los datos original para de extraer el paralelismo en dicho programa.

**Teorema 3.1.** La transformación unimodular de un bucle anidado L definida por una matriz U (unimodular) es válida si y solo si dU > 0 para cada vector distancia d de L [18, Theorem 3.1].

Si un bucle en el programa transformado no lleva la dependencia, éste puede ser ejecutado en paralelo.

# 3.4.3. Procedimiento

Esta sección tiene como objetivo plantear el procedimiento para transformar un nido de bucles anidados (perfecto) mediante matrices de transformación unimodulares, además de brindar un ejemplo para ilustrarlo.

- 1. Encontrar todos los vectores distancia d.

- 2. Seleccionar la matriz de transformación U.

- 3. Verificar la legalidad de la transformación, dU > 0 para cada vector distancia d.

- 4. Calcular el nuevo vector de iteración  $\mathbf{y} = (y_1, y_2, \dots, y_m), \mathbf{x} = \mathbf{y}(\mathbf{U}^{-1})^t$ .

- 5. Expresar los límites del espacio de iteración original en forma de politopo,  $xA \le b$

- 6. Calcular el nuevo espacio de iteración,  $y(U^{-1})^t A \le b$ .

- 7. Resolver el sistema de desigualdades aplicando el método de eliminación de *Fourier-Motzkin* [4], para encontrar los nuevos límites inferiores y superiores de y.

- 8. Reemplazar x por y en el cuerpo del nido de bucles (ahora H(y)) y en los nuevos límites de los bucles for.

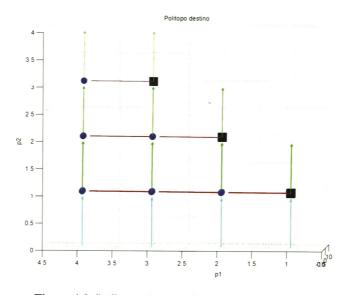

Llamaremos politopo destino al espacio de iteración del nido de bucles resultante después de realizar una transformación.

# Ejemplo 3.1

Transformar el siguiente nido de bucles con la matriz unimodular  $U = \begin{pmatrix} 1 & 1 \\ 0 & 1 \end{pmatrix}$ :

for

$$x_1 = 2, N, 1$$

do

for  $x_2 = 2, N, 1$  do

$A(x_1, x_2) = A(x_1 - 1, x_2) + A(x_1, x_2 - 1)$

end for

end for

Para resolver este ejemplo, seguiremos el procedimiento antes mencionado:

Encontrar todos los vectores distancia d.

Podemos observar que existen dos dependencias en el cuerpo de los bucles. El pri-

mer vector distancia  $\mathbf{d}_1$  se extrae de  $A(x_1, x_2)$  y  $A(x_1-1, x_2)$ ;  $\mathbf{d}_1 = (x_1-(x_1-1), x_2-x_2) = (1,0)$ . El segundo vector distancia  $\mathbf{d}_2$  se extrae de  $A(x_1, x_2)$  y  $A(x_1, x_2-1)$ ;

$\mathbf{d}_2 = (x_1 - x_1, x_2 - (x_2 - 1)) = (0, 1).$

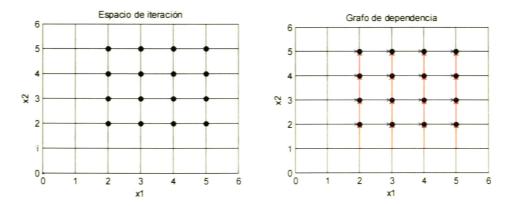

La matriz distancia es  $\mathcal{D} = \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}$ . En la figura 4.8 se representa la dependencias  $\mathbf{d}_1$  y  $\mathbf{d}_2$  en azul y rojo respectivamente.

2. Seleccionar la matriz de transformación U.

La matriz unimodular que se utilizará es  $\mathbf{U} = \begin{pmatrix} 1 & 1 \\ 0 & 1 \end{pmatrix}$

3. Verificar la legalidad de la transformación, dU > 0 para cada vector distancia d.

$$\mathbf{d}_1\mathbf{U} = (1,0) \begin{pmatrix} 1 & 1 \\ 0 & 1 \end{pmatrix} = (1,1) > \mathbf{0}$$

$$\mathbf{d}_2\mathbf{U} = (0,1) \begin{pmatrix} 1 & 1 \\ 0 & 1 \end{pmatrix} = (0,1) > \mathbf{0}$$

Como d<sub>1</sub>U y d<sub>2</sub>U son lexicográficamente positivos la transformación es legal.

4. Calcular el nuevo vector de iteración  $\mathbf{y} = (y_1, y_2, \dots, y_m)$ , mediante  $\mathbf{x} = \mathbf{y}\mathbf{U}^{-1}$

Para esto necesitamos calcular  $\mathbf{U}^{-1} = \begin{pmatrix} 1 & -1 \\ 0 & 1 \end{pmatrix}$ ,

ahora

$$\mathbf{x} = \mathbf{y}\mathbf{U}^{-1} = (x_1, x_2) = (y_1, y_2) \begin{pmatrix} 1 & -1 \\ 0 & 1 \end{pmatrix} = (y_1, -y_1 + y_2).$$

Expresar los límites del espacio de iteración original en forma de politopo, xA ≤

b.

El espacio de iteración original consiste en todos los vectores enteros  $(x_1, x_2)$  tal que:

$$\left.\begin{array}{cccc}

2 & \leq & x_1 & \leq & N \\

2 & \leq & x_2 & \leq & N

\end{array}\right\}$$

(3.4)

De las desigualdades en 4.4 se obtienen los límites inferiores del vector de iteración  $\mathbf{x} = (x_1, x_2)$  y pueden escribirse como

$$\left.\begin{array}{ccc} 2 & \leq & x_1 \\ 2 & \leq & x_2 \end{array}\right\}$$

**37**

o en forma matricial como

$$(2,2) \leq (x_1,x_2) \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix} \tag{3.5}$$

De manera similar, de las desigualdades en 4.4 dan los límites inferiores del vector de iteración  $\mathbf{x} = (x_1, x_2)$  y pueden escribirse como

$$x_1 \leq N \\ x_2 \leq N$$

o en forma matricial como

$$(x_1,x_2)\begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix} \leq (N,N)$$

(3.6)

De las ecuaciones 3.5 podemos extraer  $\mathbf{p}=(2,2)$  y  $\mathbf{P}=\begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}$ ; de 3.6 podemos extraer  $\mathbf{q}=(N,N)$  y  $\mathbf{Q}=\begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}$ .

Ahora ya estamos en condiciones de obtener el politopo fuente  $xA \le b$ .

$$(x_1, x_2)$$

$\begin{pmatrix} -1 & 0 & 1 & 0 \\ 0 & -1 & 0 & 1 \end{pmatrix} \leq (-2, -2, N, N)$  (3.7)

Figura 3.1: Espacio de iteración y grafo de dependencia del politopo fuente.

6. Calcular el nuevo espacio de iteración,  $yU^{-1}A \le b$ .

dado que

$$A = \begin{pmatrix} -1 & 0 & 1 & 0 \\ 0 & -1 & 0 & 1 \end{pmatrix}$$

,  $b = (-2, -2, N, N)$  y  $U^{-1} = \begin{pmatrix} 1 & -1 \\ 0 & 1 \end{pmatrix}$  y  $U^{-1}A \le b$  es equivalente a:

$$(y_1, y_2)$$

$\begin{pmatrix} 1 & -1 \\ 0 & 1 \end{pmatrix}$  $\begin{pmatrix} -1 & 0 & 1 & 0 \\ 0 & -1 & 0 & 1 \end{pmatrix} \leq (-2, -2, N, N)$

$$(y_1, y_2)$$

$\begin{pmatrix} -1 & 1 & 1 & -1 \\ 0 & -1 & 0 & 1 \end{pmatrix} \leq (-2, -2, N, N)$

y finalmente

$$(-y_1, y_1 - y_2, y_1, -y_1 + y_2) \le (-2, -2, N, N)$$

(3.8)

7. Resolver el sistema de desigualdades aplicando el método de eliminación de Fourier Motzkin [4], para encontrar los nuevos límites inferiores y superiores de y.

De 3.8 se extraen las siguientes desigualdades:

Resolviendo para y<sub>1</sub>

$$max(2, y_2 - N) \le y_1 \le min(N, y_2 - 2)$$

Resolviendo para y<sub>2</sub>

$$4 \le y_2 \le 2N$$

8. Reemplazar x por y en el cuerpo del nido de bucles (ahora H(y)) y en los nuevos límites de los bucles For.

El programa destino resultante es el siguiente:

for

$$y_2 = 4, 2N, 1$$

do

for  $y_1 = max(2, y_2 - N), min(N, y_2 - 2), 1$  do

$x_1 = y_1;$

$x_2 = -y_1 + y_2;$

$A(x_1, x_2) = A(x_1 - 1, x_2) + A(x_1, x_2 - 1);$

end for

end for

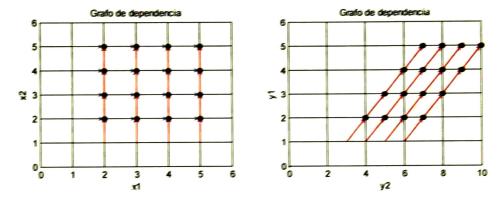

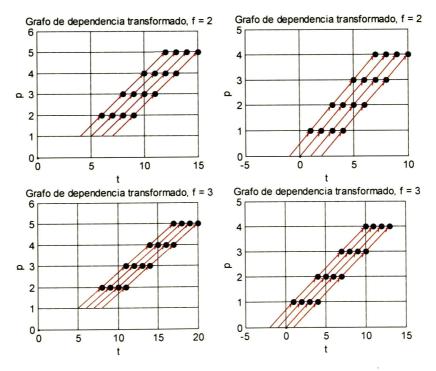

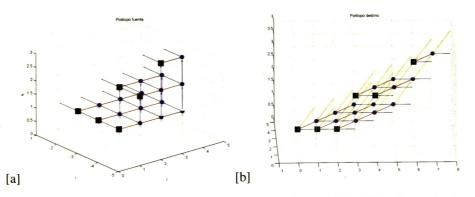

Figura 3.2: Grafo de dependencia del politopo fuente (izquierda) y del politopo destino (derecha).

Como el bucle externo lleva la dependencia, debe ser ejecutado de manera secuencial; mientras que, el bucle interno puede ser ejecutado en paralelo.

# 3.4.4. Transformaciones elementales

## 3.4.4.1. Permutación

La matriz de permutación parte de la matriz identidad y después se realizan intercambios entre sus filas. Por ejemplo la matriz  $\mathbf{U} = \begin{pmatrix} 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \end{pmatrix}$  en donde se intercambian

las filas 1 y 3. Si se tiene un vector distancia  $\mathbf{d} = (2,1,-1)$ , esta transformación no será legal, ya que  $\mathbf{dU} = (-1,1,2)$  es lexicográficamente negativo.

### 3.4.4.2. Inversión